M00101167P

# The Automatic Implementation Of A Dynamic Load Balancing Strategy Within Structured Mesh Codes Generated Using A Parallelisation Tool

Jacqueline Nadine Rodrigues

A thesis submitted in partial fulfilment of the requirement of the University of Greenwich for the Degree of Doctor of Philosophy

March 2003

Parallel Processing Research Group School of Computing and Mathematical Science University of Greenwich London, UK

I certify that this work has not been accepted in substance for any degree, and is not concurrently submitted for any degree other than that of Doctor of Philosophy (PhD) of the University of Greenwich. I also declare that this work is the result of my own investigations except where otherwise stated.

### Acknowledgements

I would kindly like to thank several people for all of their help and support throughout this period of research.

In particular, I would like to take this opportunity to thank my supervisors, Dr Steve Johnson, Dr Cos Ierotheou and Professor Mark Cross, for their invaluable help and understanding they have given me.

I would also like to thank my colleagues Dr Peter Leggett, Dr Emyr Evans and Dr Chris Walshaw, who have assisted me in various degrees in the completion of this thesis.

I appreciate all the years of effort and skill that have gone into developing CAPTools, without which this research would probably not have been undertaken.

I would also like to acknowledge my sponsers: the EPSRC and the University of Greenwich.

Finally, I would like to thank my family and friends for the endless encouragement that they have shown me over the years.

In memory of TC.

#### Abstract

This research demonstrates that the automatic implementation of a dynamic load balancing (DLB) strategy within a parallel SPMD (single program multiple data) structured mesh application code is possible. It details how DLB can be effectively employed to reduce the level of load imbalance in a parallel system without expert knowledge of the application. Furnishing CAPTools (the Computer Aided Parallelisation Tools) with the additional functionality of DLB, a DLB parallel version of the serial Fortran 77 application code can be generated quickly and easily with the press of a few buttons, allowing the user to obtain results on various platforms rather than concentrate on implementing a DLB strategy within their code. Results show that the devised DLB strategy has successfully decreased idle time by locally increasing/decreasing processor workloads as and when required to suit the parallel application, utilising the available resources efficiently.

Several possible DLB strategies are examined with the understanding that it needs to be generic if it is to be automatically implemented within CAPTools and applied to a wide range of application codes. This research investigates the issues surrounding load imbalance, distinguishing between processor and physical imbalance in terms of the load redistribution of a parallel application executed on a homogeneous or heterogeneous system. Issues such as where to redistribute the workload, how often to redistribute, calculating and implementing the new distribution (deciding what data arrays to redistribute in the latter case), are all covered in detail, with many of these issues common to the automatic implementation of DLB for unstructured mesh application codes.

The devised DLB Staggered Limit Strategy discussed in this thesis offers flexibility as well as ease of implementation whilst minimising changes to the user's code. The generic utilities developed for this research are discussed along with their manual implementation upon which the automation algorithms are based, where these utilities are interchangeable with alternative methods if desired. This thesis aims to encourage the use of the DLB Staggered Limit Strategy since its benefits are evidently significant and are now easily achievable with its automatic implementation using CAPTools.

# Contents

| Contents | 5i                                                         |

|----------|------------------------------------------------------------|

| Figures  | ix                                                         |

| Chapter  | 1 Introduction1                                            |

| 1.1      | Introduction To The Problem1                               |

| 1.2      | Structured Mesh Codes                                      |

| 1.3      | Serial Processing4                                         |

| 1.4      | Shared Memory Systems (SMS) And Distributed Memory Systems |

|          | (DMS)5                                                     |

| 1.5      | Parallel Processing                                        |

| 1.6      | Goals Of Parallelisation7                                  |

| 1.6.     | 1 Challenges Involved In Parallelisation7                  |

| 1.7      | Parallelisation Techniques8                                |

| 1.7.     | 1 Manual Parallelisation                                   |

| 1.7.     | 2 Parallelising Compilers                                  |

| 1.7.     | 3 Parallel Libraries 10                                    |

| 1.7.     | 4 Parallelisation Tools 11                                 |

| 1.8      | Computer Aided Parallelisation Tools (CAPTools)11          |

| 1.9      | Processor Communication                                    |

| 1.10     | Parallel Inefficiencies                                    |

| 1.11     | Load Imbalance                                             |

| 1.12     | 1.1 'Processor' Imbalance                                  |

| 1.1      | 1.2 'Physical' Imbalance                                   |

| 1        | .11.2.1 Geometry Of The Problem                            |

| 1        | .11.2.2 Physical Characteristics Of The Problem            |

| 1        | .11.2.3 Other Types Of Physically Imbalanced Problems      |

| 1.12     | Load Balancing                                             |

| 1.12     | 2.1 Dynamic Scheduling On A SMS                            |

| 1.12.2   | Task Balancing25                                                  |

|----------|-------------------------------------------------------------------|

| 1.12.3   | SPMD Static Load Balancing (SLB)                                  |

| 1.12.4   | SPMD Dynamic Load Balancing (DLB)                                 |

| 1.13 Mo  | tivation For Research                                             |

| 1.14 Cu  | rent Strategies And Issues Relating To Dynamic Load Balancing. 31 |

| 1.14.1   | Where To Redistribute The Workload                                |

| 1.14.2   | Frequency Of When To Redistribute The Workload                    |

| 1.14.3   | Calculating The New Partition                                     |

| 1.14.4   | Implementing The New Partition                                    |

| 1.14.5   | Manual Implementation Vs. Automatic Implementation                |

| 1.15 Air | ns Of This Research                                               |

| 1.16 Sur | nmary                                                             |

## Chapter 2 The Dynamic Load Balancing Strategy For Structure Mesh

| Code    | s                                                             |

|---------|---------------------------------------------------------------|

| 2.1 Go  | als For The Dynamic Load Balancing Strategy40                 |

| 2.2 Th  | e Importance Of Retaining A Rectangular Partition             |

| 2.3 Sta | tic Load Balancing Strategies43                               |

| 2.4 Dy  | namic Load Balancing Strategies                               |

| 2.4.1   | The Initial Problem45                                         |

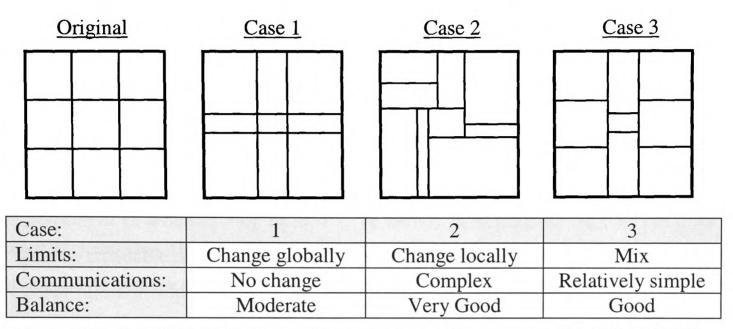

| 2.4.2   | Case 1 – Coincidental Processor Partition Range Limits        |

| 2.4.3   | Case 2 – Non-Coincidental Processor Partition Range Limits 46 |

| 2.4.4   | Case 3 – A Combination Of Case 1 And Case 2 ('Staggered       |

|         | Limits')47                                                    |

| 2.5 Th  | e Selected Dynamic Load Balancing Strategy                    |

| 2.5.1   | The DLB Staggered Limit Strategy48                            |

| 2.5.2   | The DLB Communication Structure                               |

| 2.5.3   | Inter-Processor Communication                                 |

| 2.6 Lo  | ad Migration                                                  |

| 2.7 DL  | B Issues                                                      |

| 2.7.1   | Where To Redistribute The Workload55                          |

| 2.7.2   | Frequency Of When To Redistribute The Workload 57             |

| 2.7.2.  | 1 The Influence Of Processor And Physical Imbalance           |

| 2.7.2.  | 2 A Model To Predict When To Redistribute                     |

| 2.7.    | .3 Measuring Load Imbalance                               | 63       |

|---------|-----------------------------------------------------------|----------|

| 2.7.    |                                                           |          |

| 2.8     | Implementing The New Distribution                         | 68       |

| 2.9     | Load Oscillation                                          | 70       |

| 2.10    | Goals Of The DLB Staggered Limit Strategy                 | 73       |

| 2.11    | Summary                                                   | 74       |

|         |                                                           |          |

| Chapter | r 3 Generic Dynamic Load Balancing Utilities              | 77       |

| 3.1     | Generic Utilities                                         | 77       |

| 3.2     | Initialising DLB Mode                                     | 78       |

| 3.2     | 2.1 Store Processor Neighbours                            | 78       |

| 3.2     | 2.2 Store Processor Partition Range Limits Of Neighbours  | 81       |

| 3.3     | Communicating Across Non-Coincidental Processor Partition | on Range |

|         | Limits                                                    |          |

| 3.3     | 3.1 Splitting The Communication Message                   |          |

|         | 3.3.1.1 Communication Start And End                       |          |

|         | 3.3.1.2 Communication Offsets                             |          |

|         | 3.3.1.3 New Internal Starting Address                     | 101      |

| 3.3     | 3.2 Splitting Buffered And Unbuffered Communications      | 102      |

| 3.3     |                                                           |          |

| 3.3     | 3.4 'Special' DLB Communications                          | 112      |

| 3.3     | 3.5 Testing The DLB Communication Utilities               | 114      |

| 3.4     | Determine When To Redistribute                            | 117      |

| 3.5     | Calculate The New Processor Partition Range Limits        | 119      |

| 3.5     | 5.1 Calculating The New Workload On Each Processor        | 120      |

| 3.5     | 5.2 Evaluating The New Processor Partition Range Limits   | 132      |

| 3.5     | 5.3 Adjusting The Processor Timings                       | 135      |

| 3.5     | 5.4 Processing Subsequent Partitioned Dimensions          |          |

| 3.5     |                                                           |          |

| 3.5     | 5.6 General Overview                                      | 151      |

| 3.6     | Validate New Distribution                                 |          |

| 3.7     | Migrating Data To Satisfy The New Partition               |          |

| 3.7     | 7.1 Starting Address Of The Migrated Data                 | 155      |

| 3.7.2   | 2 Starting Index And Stride Of The Migration And Stag       | gered |

|---------|-------------------------------------------------------------|-------|

|         | Dimensions                                                  | 157   |

| 3.7.    | 3 Migration Length                                          | 158   |

| 3.7.4   | 4 Type Of Data Being Migrated                               | 160   |

| 3.7.    | 5 The Load Migration Algorithm For CAP_MIGRATE              | 160   |

| 3.7.    | 6 The Load Migration Algorithm For CAP_DLB_MIGRATE          | 166   |

| 3.7.    | 7 General Overview Of The Migration Utilities               | 168   |

| 3.8     | Multi-Buffering                                             | 169   |

| 3.9     | Updating The Processor Partition Range Limits               | 172   |

| 3.10    | Overview Of The DLB Utilities                               | 174   |

| 3.11    | Summary                                                     | 176   |

|         |                                                             |       |

| Chapter | r 4 Manually Implementing The DLB Staggered Limit Str       | ategy |

| ١       | Within A CAPTools Generated Parallel Structured Mesh Code   | 179   |

| 4.1     | The Implementation Algorithm                                | 179   |

| 4.2     | Setting Up The DLB Parallel Code                            | 180   |

| 4.2     | .1 The Staggered And Non-Staggered Dimensions               | 180   |

| 4.2     | .2 Initialising DLB Mode                                    | 181   |

| 4.3     | Converting Existing Communications Into DLB Communications. | 182   |

| 4.4     | Where To Redistribute The Workload                          | 191   |

| 4.5     | Determine When To Redistribute                              | 195   |

| 4.6     | Calculating The New Processor Partition Range Limits        | 195   |

| 4.7     | Implementing The New Distribution                           | 196   |

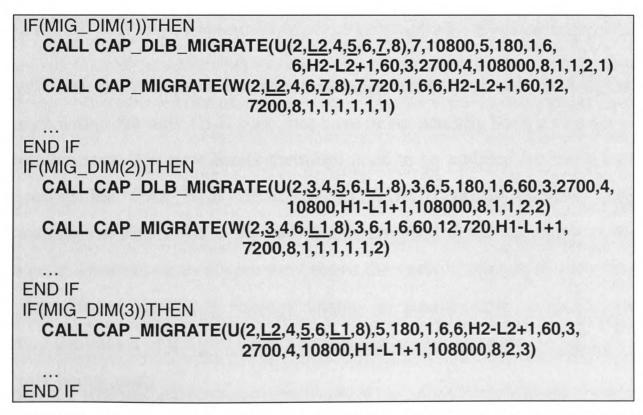

| 4.7     | Construct The Necessary Migration Calls                     | 196   |

| 4.7     | 2.2 Reassign The Limits                                     | 200   |

| 4.7     |                                                             |       |

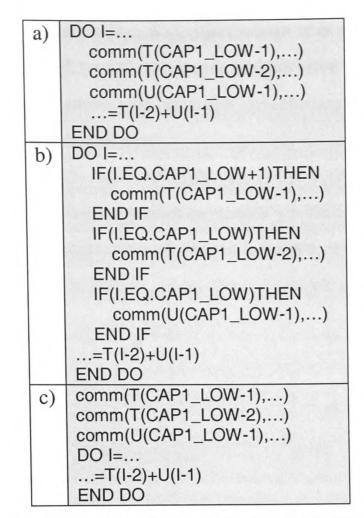

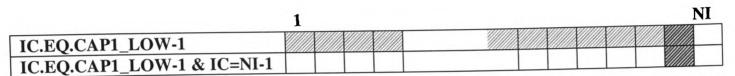

| 2       | 4.7.3.1 Identifying Potential Communications To Duplicate   |       |

| 4.8     | Example DLB Code                                            |       |

| 4.9     | Results And Observations                                    |       |

| 4.9     |                                                             |       |

| 4.9     | D.2 The APPLU-1.4 And ARC3D Codes                           | 219   |

| 4.9     | D.3 The SEA Code                                            | 220   |

| 4.10    | Summary                                                     | 224   |

| Chapter | 5 Automatically Implementing The DLB Staggered Limit Strategy     |

|---------|-------------------------------------------------------------------|

| W       | ithin CAPTools Generated Structured Mesh Codes                    |

| 5.1     | Automation Within CAPTools                                        |

| 5.2     | Adding DLB To The Functionality Of CAPTools                       |

| 5.3     | Fixing The Staggered Dimension                                    |

| 5.4     | New Data Structures Needed For Automation                         |

| 5.5     | Overview Of Automatically Implementing The DLB Staggered Limit    |

|         | Strategy                                                          |

| 5.6     | Identifying And Converting Existing Communications Into DLB       |

|         | Communications                                                    |

| 5.6.    | 1 Identifying Those Communications To Be Converted                |

| 5.6.    | 2 Converting Communications Into DLB Communications               |

| 5.6.    | 3 Implicit Partitioning Of Communicated Data And 'Special' DLB    |

|         | Communications241                                                 |

| 5.7     | Inserting The DLB Code                                            |

| 5.7.    |                                                                   |

| 5.7.    |                                                                   |

| 5.8     | Inserting The Migration Calls                                     |

| 5.8.    |                                                                   |

| 5.8.    |                                                                   |

| 5       | 5.8.2.1 Setting Up The Starting Address For The Migrated Data 258 |

| 5       | 5.8.2.2 Setting Up The Starting Index And Stride For The Migrated |

|         | Data In The Migration Dimension And The Staggered                 |

|         | Dimension                                                         |

| 5       | 5.8.2.3 Setting Up The Stride And Number Of Strides               |

| 5       | 5.8.2.4 Completing The Migration Call By Setting Up The Type Of   |

|         | Data Being Migrated And The Migration Dimension                   |

| 5.8     | <b>-</b>                                                          |

|         | Is 1D-Mapped                                                      |

| 5.8     |                                                                   |

|         | Is Unpartitioned                                                  |

| 5.9     | Updating The Processor Partition Range Limits                     |

| 5.10    | Duplicating Overlap Communications                                |

| 5.1     | 0.1 Identifying Potential Overlap Communications To Duplicate 273 |

| 5.10.2 Testing The Us           | age Statements Of The Identified Overlap     |

|---------------------------------|----------------------------------------------|

| Communications.                 |                                              |

| 5.10.3 New Communicat           | ions For Assigned Overlaps                   |

| 5.11 Results And Observation    | ons                                          |

| 5.11.1 Overview Of Cod          | es                                           |

| 5.12 Summary                    |                                              |

|                                 |                                              |

| Chapter 6 Automatically Im      | plementing A Dynamic Load Balancing          |

| Strategy Within A CAP           | Tools Generated Unstructured Mesh Code       |

| ******************************* |                                              |

|                                 | des                                          |

| 6.2 The Parallelisation Of      | An Unstructured Mesh Code Using CAPTools     |

|                                 |                                              |

| 6.3 Load Imbalance Withi        | n An Unstructured Mesh Code 296              |

| 6.4 Dynamic Load Balanc         | ing                                          |

| 6.4.1 Where To Redistr          | ibute The Workload 297                       |

| 6.4.2 Determine When            | To Redistribute                              |

| 6.4.3 Calculating The N         | New Distribution                             |

| 6.4.4 Implementing Th           | e New Distribution                           |

| 6.5 Summary                     |                                              |

|                                 |                                              |

| -                               | urther Work 300                              |

|                                 | ty And Future Improvements                   |

| 7.2 Final Remarks               |                                              |

|                                 |                                              |

| <b>F F</b>                      | s Parallelisation Strategy And Communication |

|                                 |                                              |

|                                 | 304                                          |

|                                 | Structured Mesh Codes                        |

|                                 | tions                                        |

|                                 | nunication                                   |

|                                 | inications                                   |

|                                 | Гороlogy                                     |

| A.3.3 Generic Commu             | nication Utilities                           |

|       | A.3.3.1        | Send And Receive Communications                             | . 320 |

|-------|----------------|-------------------------------------------------------------|-------|

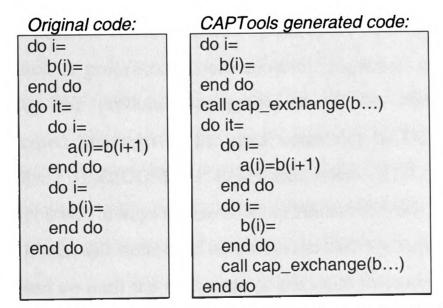

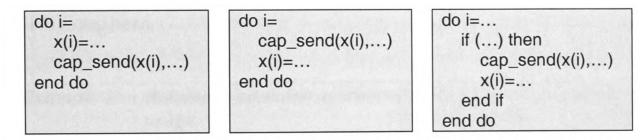

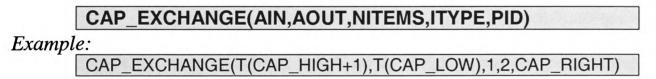

|       | A.3.3.2        | Exchange Communications                                     | . 323 |

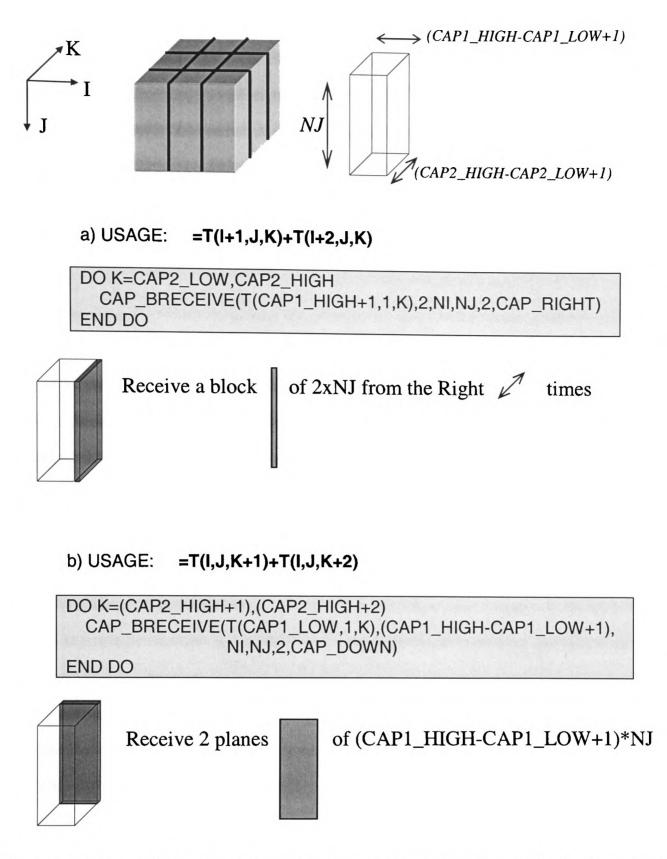

|       | A.3.3.3        | Buffered Communications                                     | . 325 |

|       | A.3.3.4        | Multi-Dimensional Communications                            | . 327 |

|       | A.3.3.5        | Broadcast Communications                                    | . 330 |

|       | A.3.3.6        | 6 Commutative Communications                                | . 332 |

| A.4   | Com            | piling And Executing CAPTools Generated Parallel Code       | . 333 |

| A.5   | Sum            | mary                                                        | . 334 |

|       |                |                                                             |       |

| Apper | ndix B         | CAPTools Algorithms And Data Structures                     | . 335 |

| B.1   | The            | Parallelisation Of A Structured Mesh Code Using CAPTools    | . 335 |

| B.2   | Load           | ding The Serial Code                                        | . 336 |

| B.3   | The            | Call Graph                                                  | . 337 |

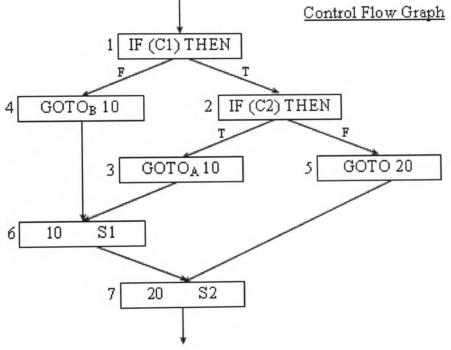

| B.4   | The            | Control Flow Graph                                          | . 342 |

| В     | 8.4.1          | Pre- And Post- Dominator Blocks                             | . 346 |

| B.5   | Nest           | ting Information                                            | . 348 |

| B.6   | Dep            | endence Analysis                                            | . 349 |

| E     | 8.6.1          | Dependence Types                                            | . 350 |

| E     | 8.6.2          | Control Dependence Calculation                              | . 351 |

| E     | 8.6.3          | Dependence Depth                                            | . 354 |

| E     | 8.6.4          | Loop Normalisation And Induction Variable Substitution      | . 355 |

| E     | 8.6.5          | Dependence Testing                                          | . 356 |

| E     | 8.6.6          | Routine Dependence Graph                                    | . 360 |

| E     | 8.6.7          | Interprocedural Dependence Analysis (Routine Input And Outp | out). |

|       |                |                                                             | . 361 |

| E     | 8.6.8          | Value Based Covering Sets                                   | . 362 |

| B     | 8.6.9          | User Interaction In Dependence Analysis                     | . 363 |

| Е     | 8.6.10         | Symbolic Variable Manipulation                              | . 364 |

|       | B.6.10         | .1 Symbolic Variable Equality                               | . 364 |

|       | <b>B.6.1</b> 0 | .2 Using Symbolic Variables                                 | . 365 |

|       | B.6.10         | .3 Symbolic Variable Manipulation Utilities                 | . 367 |

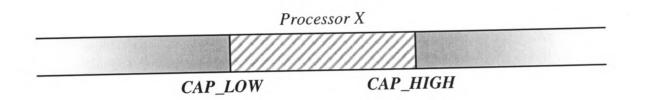

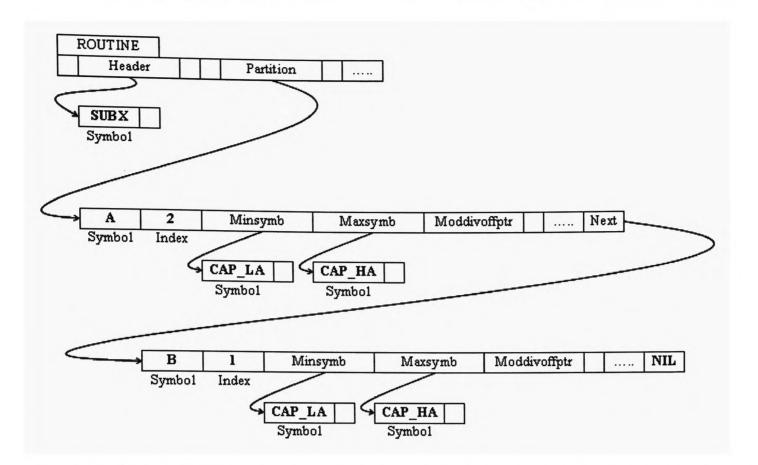

| B.7   | Data           | a Partitioning                                              | . 369 |

| E     | 3.7.1          | Dimension Mapping Between Routines (Modulus And Division    | n)    |

|       |                |                                                             | . 376 |

| B.7.2 The Partition Data Structure                                 |

|--------------------------------------------------------------------|

| B.8 Execution Control Masks                                        |

| B.9 Communications                                                 |

| B.9.1 The Calculation And Generation Of Communications             |

| B.9.1.1 Calculation Of Communication Requests                      |

| B.9.1.2 The Communication Of Implicitly Partitioned Data           |

| B.9.1.3 Conflict Broadcasts                                        |

| B.9.1.4 Migration Of Communication Requests                        |

| B.9.1.5 Merging Communication Requests                             |

| B.9.1.6 Generation Of Communications                               |

| B.9.2 Communication Data Structures                                |

| B.10 Reduced Memory                                                |

| B.11 Partition Next Dimension (Multi-Dimensional Partitioning)     |

| B.12 Generating And Saving The Final Parallel Code                 |

| B.13 Summary                                                       |

| Appendix C Automatically Generated DLB Parallel Version Of The FAB |

| Code                                                               |

| Bibliography                                                       |

# Figures

| Figure 1.1: Goals that are used to parallelise a code7                               |

|--------------------------------------------------------------------------------------|

| Figure 1.2: Some of the challenges encountered when using parallel processing 8      |

| Figure 1.3: Criteria used by CAPTools to effectively parallelise industrial and      |

| scientific application codes onto massively parallel systems                         |

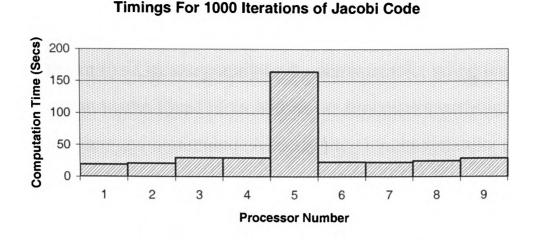

| Figure 1.4: Example illustrating the difference between the processor timings for    |

| 1000 iterations of the Jacobi Iterative Solver used on a heterogeneous system        |

| of processors, where the overall time is that of the slowest processor               |

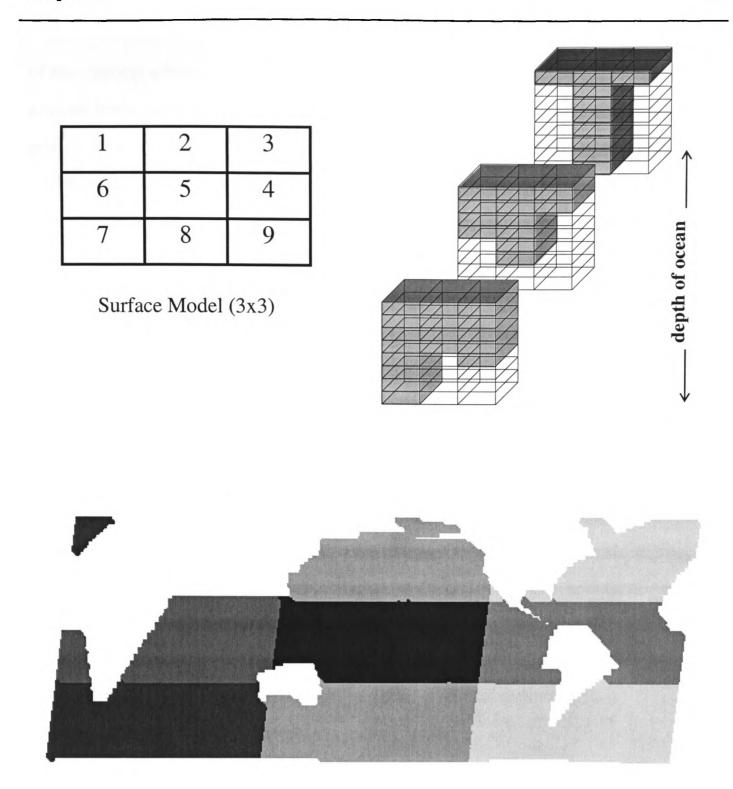

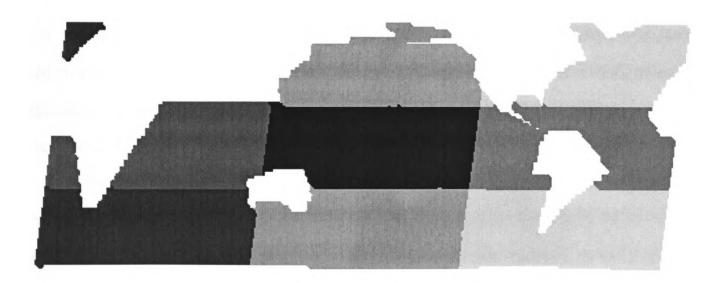

| Figure 1.5: Example showing the Earth partitioned onto 9 processors, each            |

| represented by different colourings, where each processor owns a varying             |

| depth of ocean upon which to compute on. Africa and Europe are situated to           |

| the left and the Americas are situated to the right                                  |

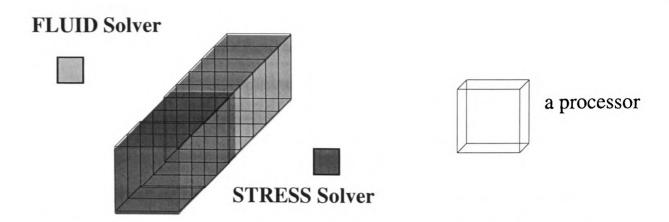

| Figure 1.6: Example illustrating an intermediate stage in the solidification process |

| of a rectangular bar, in which approximately half the cells are solid and half       |

| are liquid (for which different solvers are used), where the bar is cooled from      |

| one end                                                                              |

| Figure 1.7: Issues relating to the implementation of Dynamic Load Balancing31        |

|                                                                                      |

| Figure 1.8: The four key aims of this research                                       |

|                                                                                      |

| Figure 1.8: The four key aims of this research                                       |

| Figure 1.8: The four key aims of this research                                       |

| Figure 1.8: The four key aims of this research                                       |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

| <ul> <li>Figure 1.8: The four key aims of this research</li></ul>                    |

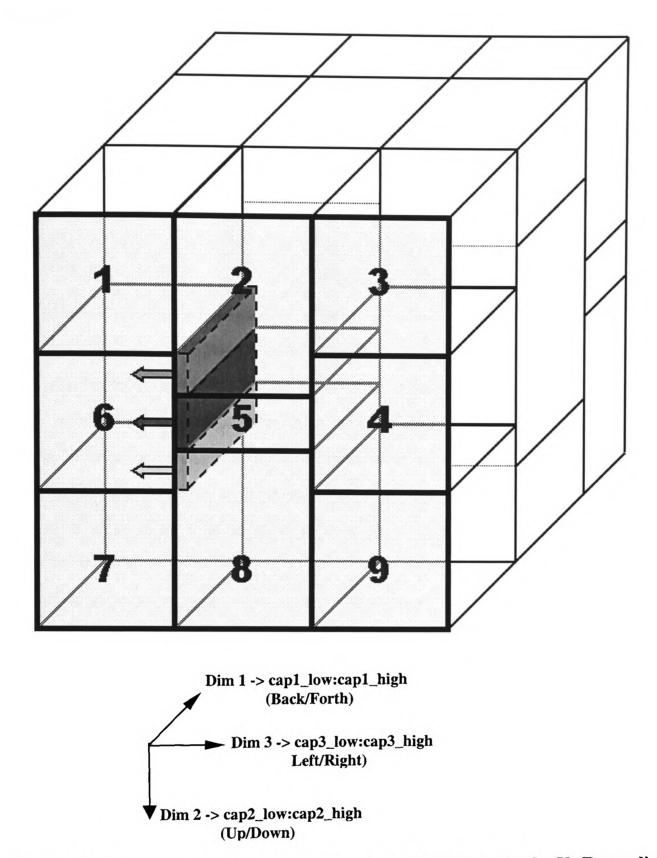

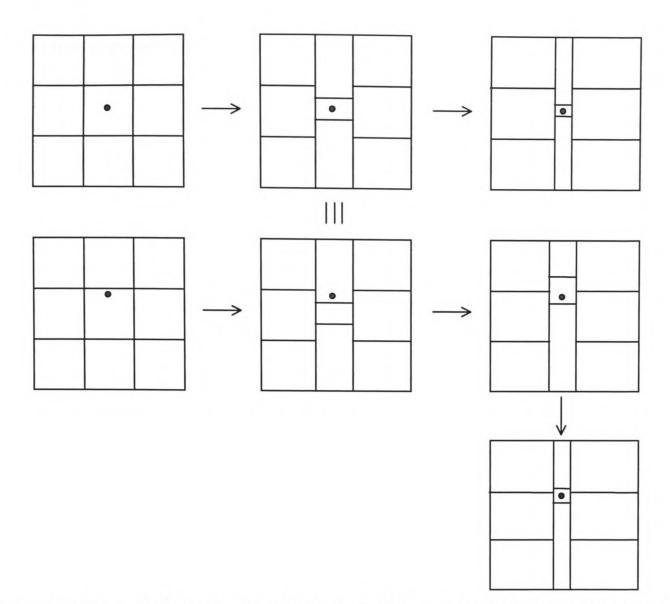

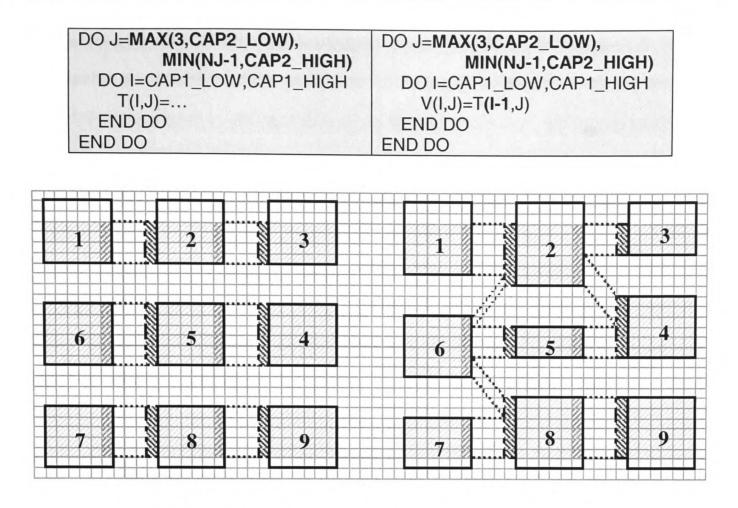

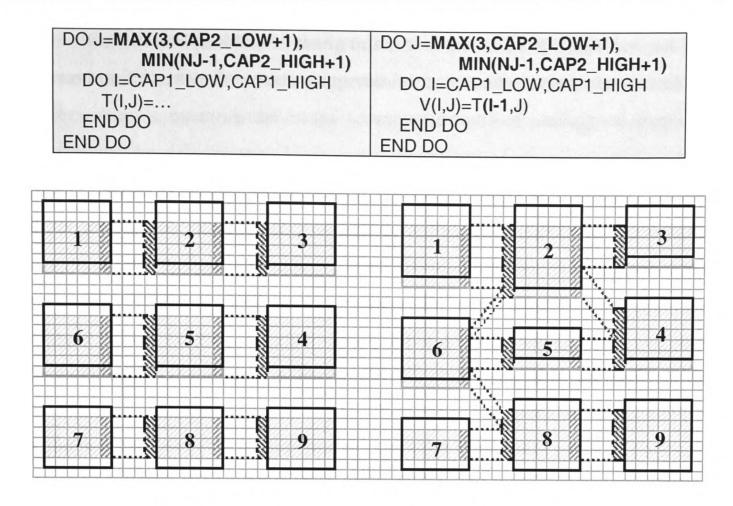

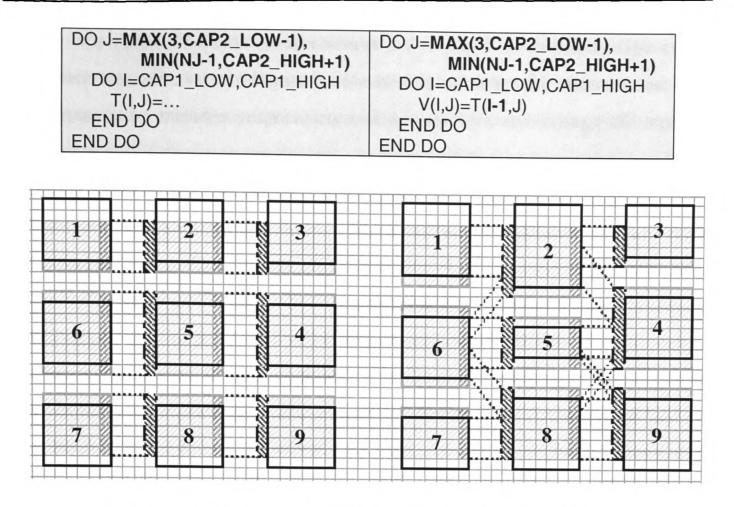

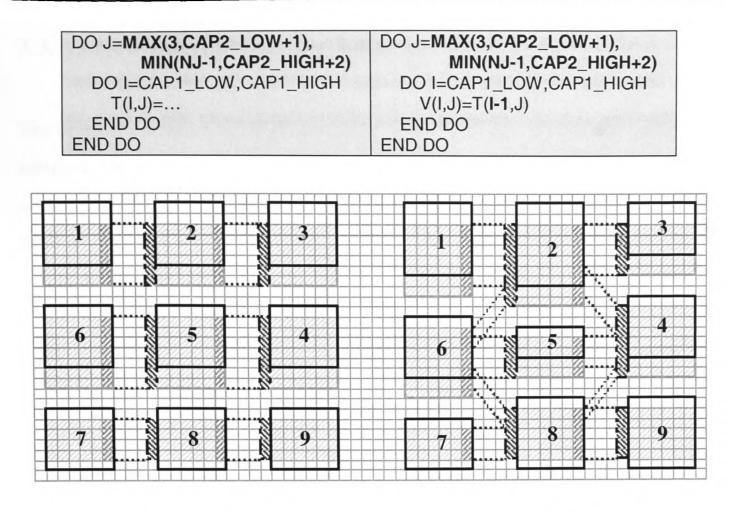

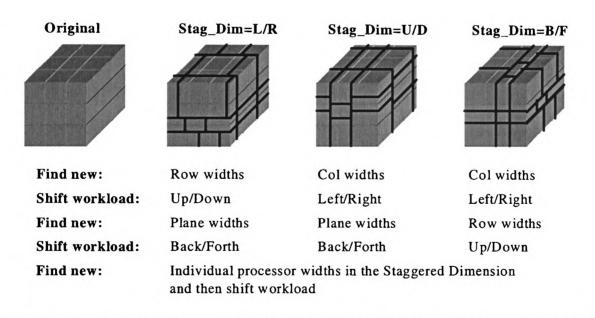

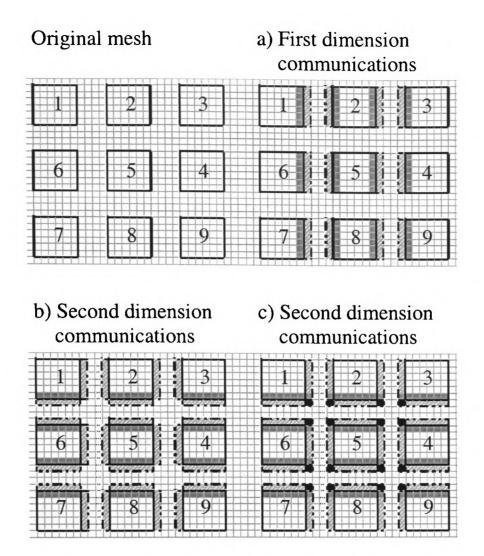

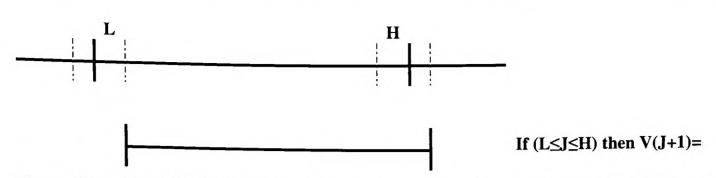

its Right. Dimension 2 is the Staggered Dimension, implying that dimensions

| 1 and 3 (the Non-Staggered Dimensions) use global processor partition range         |

|-------------------------------------------------------------------------------------|

| limits                                                                              |

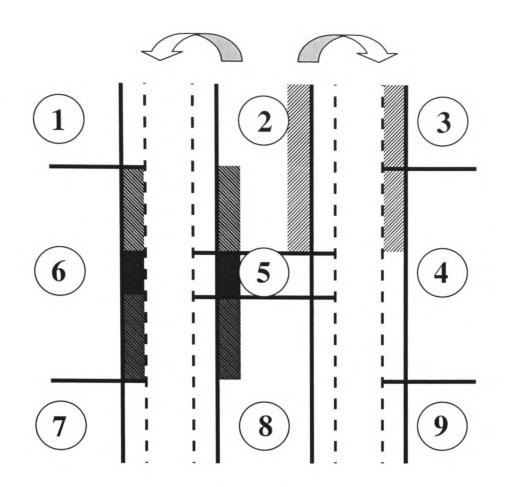

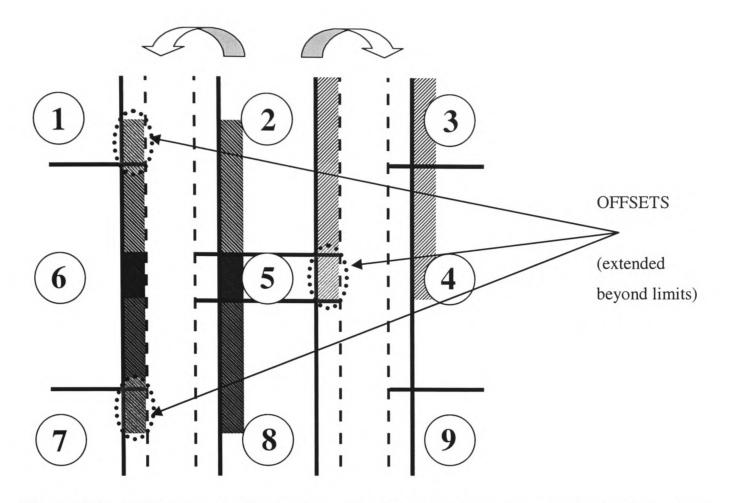

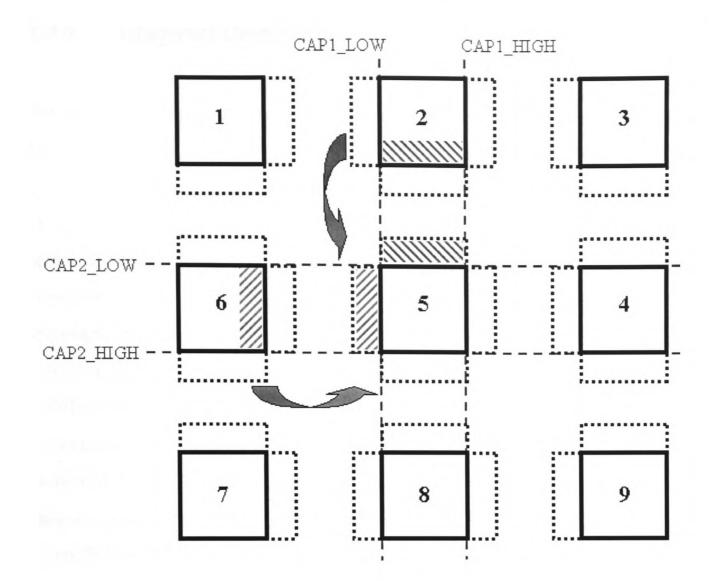

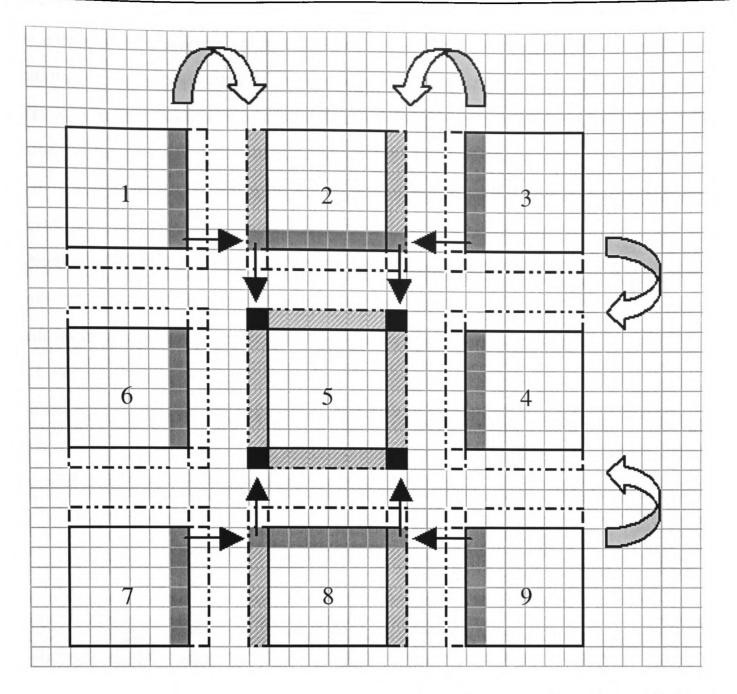

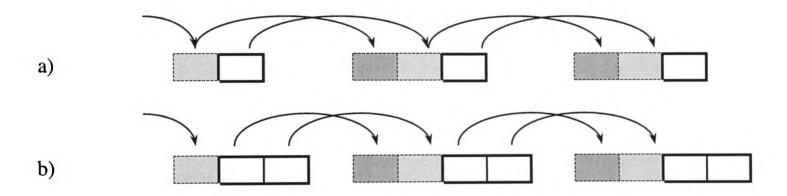

| Figure 2.5: A 2D representation of the halo update on Processor 6 from several      |

| neighbours, and not just their immediate neighbour. Also shown is the data          |

| that is sent from Processor 2 to its neighbours on the Right                        |

| Figure 2.6: A 2D example illustrating what happens when the communication           |

| extends beyond the processor partition range limits, on Processor 2 and             |

| Processor 6. The 'offset' data (from the processor limit) must be included in       |

| the communication53                                                                 |

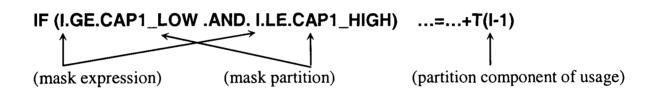

| Figure 2.7: Example illustrating a communication that is executed within an         |

| execution control mask                                                              |

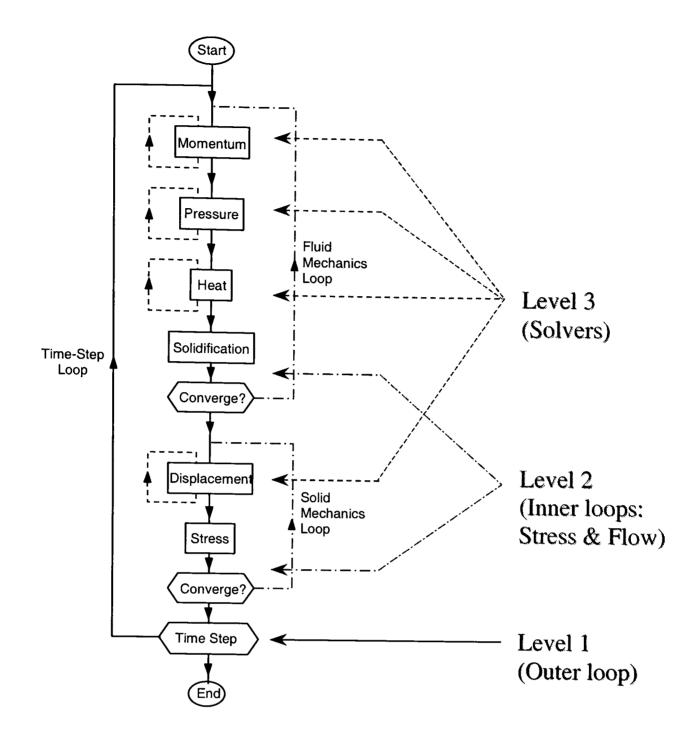

| Figure 2.8: Example illustrating the different levels in which the load could be    |

| balanced57                                                                          |

| Figure 2.9: Model of computation depicting load imbalance                           |

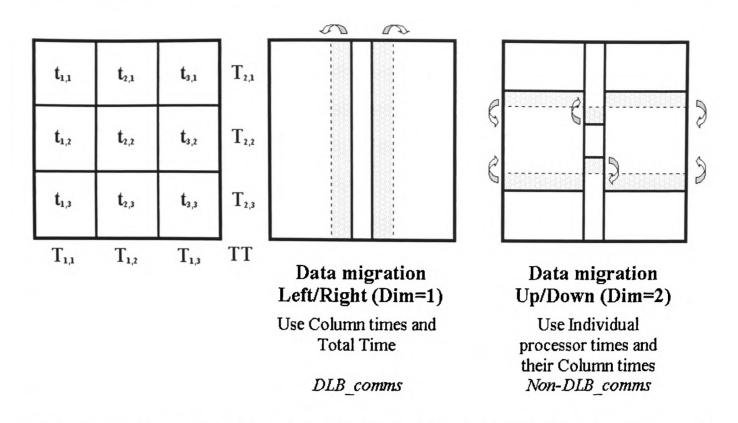

| Figure 2.10: Data migration for a two-dimensional processor topology, with          |

| global Left/Right processor partition range limits and staggered Up/Down            |

| processor partition range limits                                                    |

| Figure 2.11: Example illustrating how the load would move given the location of     |

| the heaviest cell when assuming physical imbalance73                                |

| Figure 3.1: 2D grid in which the Up/Down processor partition range limits may be    |

| staggered79                                                                         |

| Figure 3.2: Examples of what is stored in ALLNEIGHBOURS, for Figure 3.1 and         |

| Figure 2.3                                                                          |

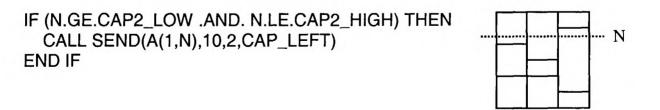

| Figure 3.3: Call statements used to internally set up the processor partition range |

| limits of all processors                                                            |

| Figure 3.4: Code used to store the processor partition range limits for each        |

| processor in the specified dimension                                                |

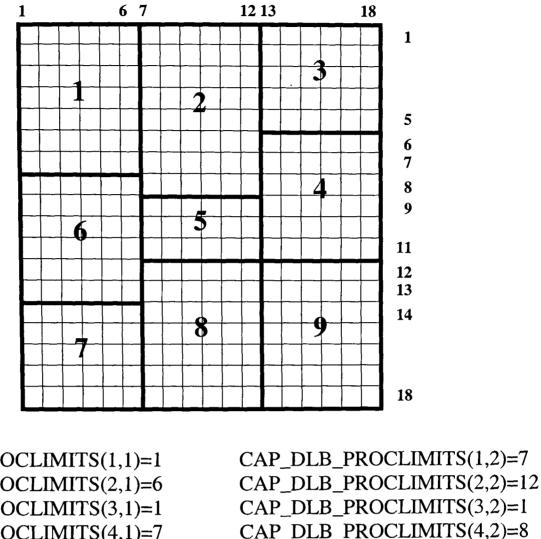

| Figure 3.5: Example in which the processor partition range limits are staggered in  |

| the Up/Down direction (second partitioned dimension). Also shown are the            |

| contents of CAP_DLB_PROCLIMITS, known by all processors, indicating                 |

| the partition range limits of each processor                                        |

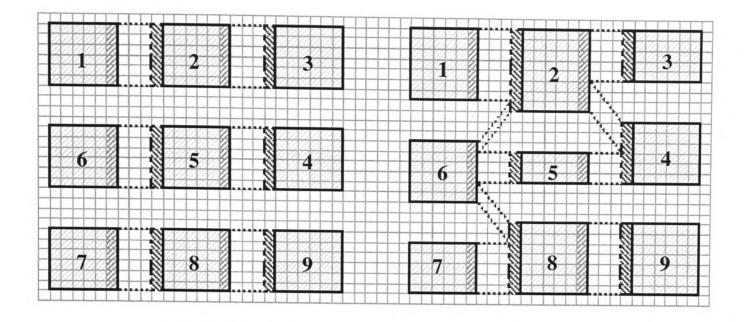

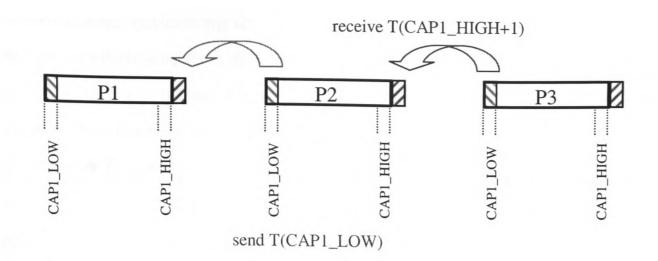

| Figure 3.6: Example demonstrating that the original communication message can       |

| be dissected into the intersection of the staggered processor partition range       |

| limits, where the new message starts from CAP2_LOW, and ends at                     |

| CAP2_HIGH. The original communication set and the new DLB                     |

|-------------------------------------------------------------------------------|

| communication set are shown, along with the message range being sent and      |

| received by each processor with their neighbouring processors                 |

| Figure 3.7: General code used to dissect original communication message       |

| Figure 3.8: Example demonstrating that the original communication message may |

| not always start from CAP2_LOW, and end at CAP2_HIGH. The original            |

| communication set and the new DLB communication set are shown, along          |

| with the message range being sent and received by each processor with their   |

| neighbouring processors91                                                     |

| Figure 3.9: The communication start and end locations for the communicating   |

| processor, where FIRST is the starting index of the communicated data in the  |

| Staggered Dimension                                                           |

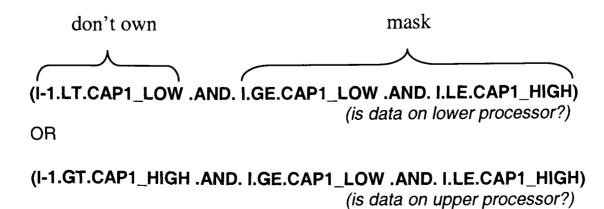

| Figure 3.10: Example demonstrating that the original communication message    |

| may be 'offset', such that a processor may assign data in their halo region,  |

| which is then needed by a neighbouring processor. The original                |

|                                                                               |

Figure 3.14: Example in which data is assigned on more than one processor, where L\_OFF and H\_OFF have different values but the same sign. .......... 100

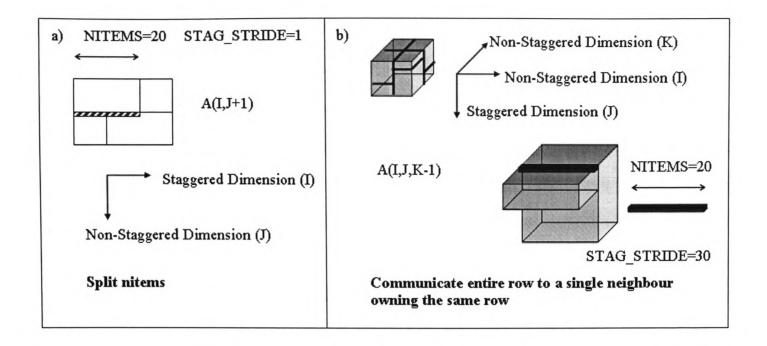

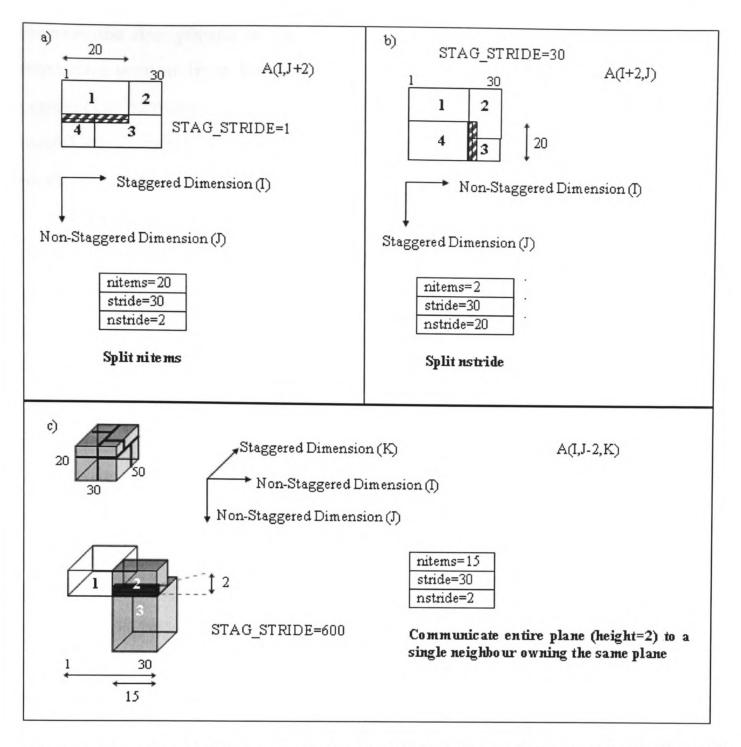

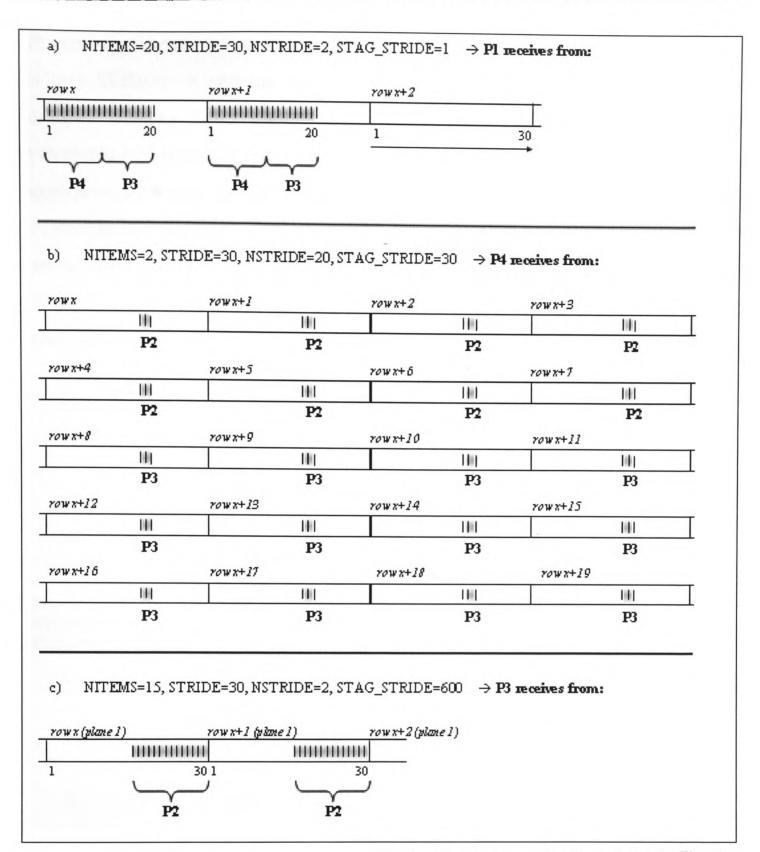

- Figure 3.16: Unbuffered DLB communications in which a) the continuous message is dissected amongst neighbouring processors (STAG\_STRIDE<NITEMS); and b) the continuous message İS communicated with a single neighbour (STAG\_STRIDE>NITEMS). In both cases the length of the first dimension is 30...... 103

Figure 3.21: Equating the strides of different dimensions for an array variable. 110

| Figure 3.24: Shown are the staggered processor partition range limits for the      |

|------------------------------------------------------------------------------------|

| processors involved in the DLB communication shown in Figure 3.23, where           |

| the internally executed low-level communications are shown                         |

| Figure 3.25: Example demonstrating a 'special' DLB communication in which          |

| only those processors owning row 8 will be involved                                |

| Figure 3.26: 'Special' DLB communications that do not dissect the                  |

| communication message but determine who to communicate with based on               |

| the execution control mask of the assigned data (passed in as FIRST) 114           |

| Figure 3.27: Example code showing the original communication between               |

| Processor 5 and Processor 4, and the new code needed when staggered limits         |

| are implemented, where Processor 5 may have to communicate with                    |

| Processors 3, 4, and 9, when using a 3x3 processor topology                        |

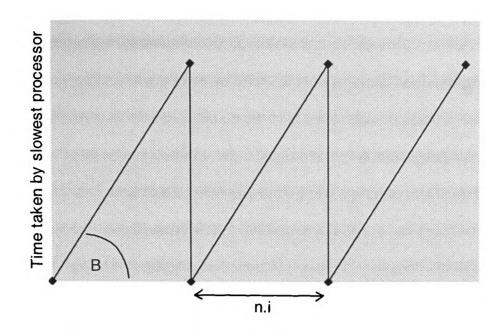

| Figure 3.28: Calculating the rate of load imbalance (B)                            |

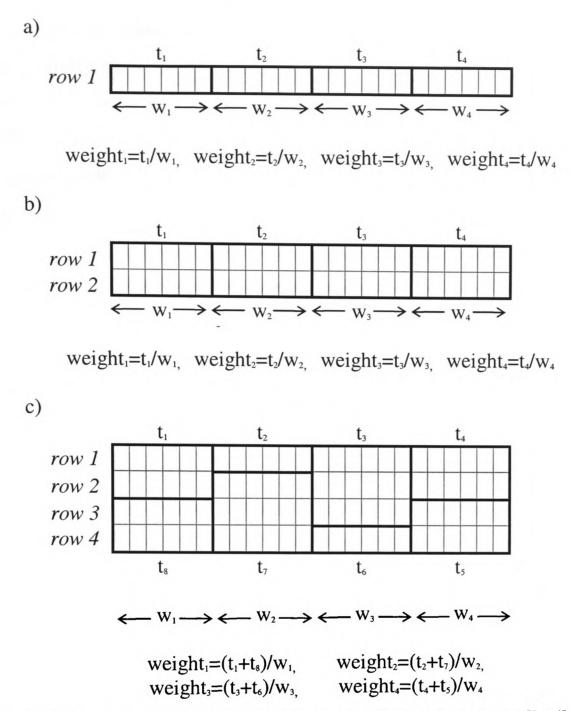

| Figure 3.29: Example showing a) a single row of cells that have been distributed   |

| onto 4 processors; b) two rows of cells that have been distributed onto 4          |

| processors; and c) four rows of cells that have been distributed onto 8            |

| processors (using a $4x2$ topology). The weight (time to process a column of       |

| cells) can be calculated using $t_p$ and $w_p$ , representing the processor timing |

| and width of cells on a processor                                                  |

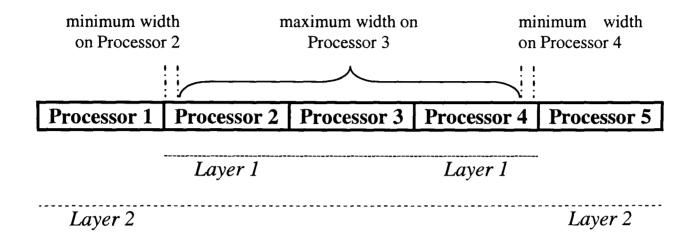

| Figure 3.30: Processor 3 can only gain cells from, or lose cells to, its immediate |

| neighbours (in Layer 1) Processor 2 and 4. The maximum number of cells             |

| that can be gained by Processor 3 is shown, taking into account the minimum        |

| width restriction on its neighbouring processors. Cells can be gained or lost      |

| to neighbours in Layer 2 in subsequent redistributions                             |

| Figure 3.31: Calculation used to determine the maximum width on each processor.    |

|                                                                                    |

| Figure 3.32: Graphical representation of the example shown in Figure 3.30, whose   |

| details are given in Table 3.5126                                                  |

| Figure 3.33: Calculation used to find the initial new distribution                 |

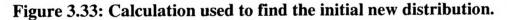

| Figure 3.34: Graphical representation of the initial distribution of the problem   |

| shown in Figure 3.32 when processor imbalance is presumed                          |

| Figure 3.35: New distribution of the problem shown in Figure 3.32 after one        |

| iteration. The calculation of the estimated timing, if given an additional cell,   |

| is shown for each processor using the initial width and timings along with the     |

| processor weights. The additional call is allocated to Processor 4 who has the      |

|-------------------------------------------------------------------------------------|

| processor weights. The additional cell is allocated to Processor 4 who has the      |

| lowest estimated timing                                                             |

| Figure 3.36: Several iterations that are used to find the new distribution of the   |

| problem shown in Figure 3.32                                                        |

| Figure 3.37: Pseudo code used to evaluate the new processor partition range limits  |

| for the processors in Figure 3.32 133                                               |

| Figure 3.38: Example of a 5x2x3 processor topology, where the processor             |

| numbers are given followed by the processor timing (in seconds) in brackets.        |

|                                                                                     |

| Figure 3.39: Amended pseudo code that is used to evaluate the new processor         |

| partition range limits for the groups of processors in Figure 3.38                  |

| Figure 3.40: Simple example showing 5 cells on a processor, where the time to       |

| process each cell is different. Using the assumption that every cell on a           |

| processor takes the same time to compute, then each cell would take 5               |

| seconds                                                                             |

| Figure 3.41: Estimate of the initial width on each processor when physical          |

| imbalance is presumed                                                               |

| Figure 3.42: Graphical representation of the initial distribution of the problem    |

| shown in Figure 3.32 when physical imbalance is presumed                            |

| Figure 3.43: The 1st iteration (assuming physical imbalance) of the distribution of |

| a cell in example Figure 3.42, given the initial distribution and the current       |

| processor widths and times. The estimated timing is calculated given the            |

| processor gains a cell from its lower neighbour (L), from its self (S), or from     |

| its upper neighbour (U), where possible142                                          |

| Figure 3.44: Remaining iterations that are used to redistribute the workload in     |

| example Figure 3.34 given that physical imbalance is assumed                        |

| Figure 3.45: Pseudo code used to determine how many cells can be gained from a      |

| neighbouring processor, in the lower and upper direction, where the                 |

| minimum width is equivalent to the width of the halo region                         |

| Figure 3.46: Pseudo code used to adjust the processor timings for the example in    |

| Figure 3.34                                                                         |

| Figure 3.47: Example using a 5x3 processor topology, where the processor            |

| numbers are shown in a), and the processor timings and staggered limits are         |

| shown in b). The Group widths and timings are shown in c)                           |

| 2                                                                                   |

| Figure 3.48: Amended pseudo code that is used to adjust the processor timings,      |

|-------------------------------------------------------------------------------------|

| which takes into account the grouping of processors and physical imbalance.         |

|                                                                                     |

| Figure 3.49: Utility used to determine whether or not to actually implement the     |

| newly calculated distribution. Migrate data in dimension only if enough cells       |

| are migrated in this dimension                                                      |

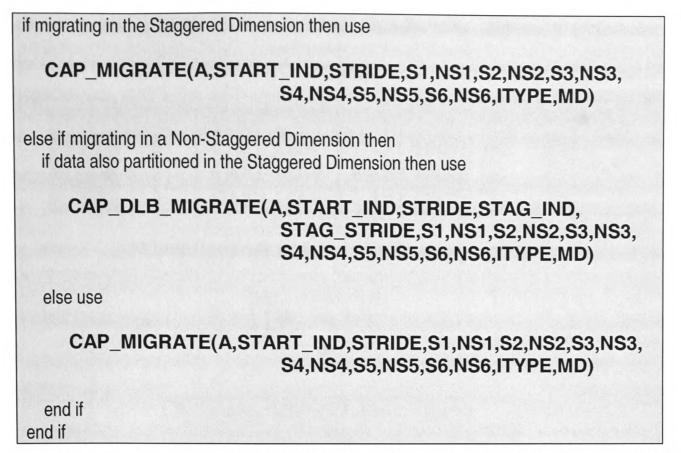

| Figure 3.50: The migration utilities that are used to migrate data in the Staggered |

| Dimension (CAP_MIGRATE), and in a Non-Staggered Dimension                           |

| (CAP_DLB_MIGRATE) 155                                                               |

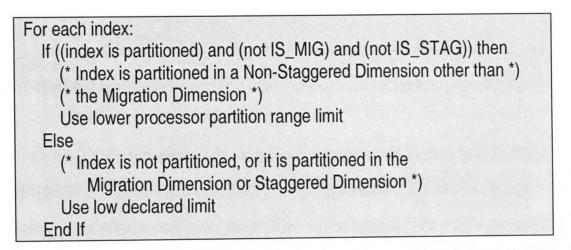

| Figure 3.51: Example illustrating the starting address of an array to be migrated,  |

| in which the low declared limit is used in all but the Staggered Dimension          |

| and the Migration Dimension157                                                      |

| Figure 3.52: Example showing how to construct the START_IND and STRIDE              |

| parameters for the Migration Dimension                                              |

| Figure 3.53: Example showing how to construct the STAG_IND and                      |

| STAG_STRIDE parameters for calls to CAP_DLB_MIGRATE 158                             |

| Figure 3.54: Example showing how to construct the S and NS parameters               |

| representing the migration length159                                                |

| Figure 3.55: Example showing how to construct the ITYPE parameter (where 2 is       |

| used to represent data of type REAL) 160                                            |

| Figure 3.56: Return the old or new processor partition range limit in either the    |

| lower (LIM=1) or upper (LIM=2) direction of the partitioned dimension D             |

| for the calling processor (CAP_PROCNUM)161                                          |

| Figure 3.57: Example illustrating various situations after load redistribution for  |

| Processor X whose old lower and upper limits are represented by $L_x$ and $H_x$     |

| respectively, and whose new lower and upper limits are represented by $L_x$         |

| and $H_x$ respectively                                                              |

| Figure 3.58: Code used to determine the amount to migrate (SECTION) and from        |

| where to begin migrating (START) for the Migration Dimension 163                    |

| Figure 3.59: Code used to determine the starting address of the internal            |

| communication (that operates in terms of bytes)                                     |

| Figure 3.60: Code used to determine the amount of continuous data to                |

| communicate internally, which shall operate in bytes                                |

| Figure 3.61: Calls to pack and unpack continuous data into and from a buffer that  |

|------------------------------------------------------------------------------------|

| are used inside the CAP_MIGRATE utility165                                         |

| Figure 3.62: Communication calls that are used internally within the               |

| CAP_MIGRATE utility, where NITEMS of continuous data (in terms of                  |

| bytes) are communicated in the specified communication direction starting          |

| from BUFF(*)                                                                       |

| Figure 3.63: Basic code that is used to identify neighbouring processors with      |

| which to communicate with                                                          |

| Figure 3.64: Code used to determine STAG_START and STAG_SECTION,                   |

| where a communication is performed with the neighbouring processor if its          |

| staggered limits overlap with the staggered limits of the migrating processor.     |

|                                                                                    |

| Figure 3.65: Code used to determine the starting address of the internal           |

| communication, and the number of continuous bytes of data to be                    |

| communicated 167                                                                   |

| Figure 3.66: Calls to pack and unpack continuous data into and from a buffer that  |

| are used inside the CAP_DLB_MIGRATE utility (which now involve                     |

| STAG_SECTION and STAG_STRIDE) 168                                                  |

| Figure 3.67: The low-level communication calls that are used internally within the |

| CAP_DLB_MIGRATE utility, where NITEMS of continuous data (in terms                 |

| of bytes) are communicated to a specific NEIGHBOUR starting from                   |

| BUFF(1)                                                                            |

| Figure 3.68: Utility used to pack multi-dimensional data into a buffer, which is   |

| called from within a migration call (CAP_MIGRATE or                                |

| CAP_DLB_MIGRATE)171                                                                |

| Figure 3.69: Utility used to unpack multi-dimensional data from a buffer, which is |

| called from within a migration call (CAP_MIGRATE or                                |

| CAP_DLB_MIGRATE)172                                                                |

| Figure 3.70: Code demonstrating how the processor partition range limits are       |

| updated after migration                                                            |

| Figure 3.71: The utility used to update the processor partition range limits after |

| migration, where the limits and the Migration Dimension have been                  |

| specified173                                                                       |

| Figure 3.72: Utility used to update the internal processor limits                  |

| Figure 4.1: The basic DLB algorithm used to implement the DLB Staggered Limit    |

|----------------------------------------------------------------------------------|

| Strategy within a parallel code                                                  |

| Figure 4.2: Illustration of a 3D problem in which different dimensions have been |

| staggered181                                                                     |

| Figure 4.3: Setting up code to run in DLB mode                                   |

| Figure 4.4: The communication involving U can be converted into a DLB            |

| communication as 1) there exists a statement involving the use of the            |

| partitioned limits and the communicated data; and 2) the communication           |

| itself involves the staggered processor partition range limits                   |

| Figure 4.5: Transformation of a communication into a DLB communication           |

| (along with information relating to the communicated data)                       |

| Figure 4.6: How to obtain FIRST when multi-dimensional arrays or 1D mapped       |

| indices are used 185                                                             |

| Figure 4.7: Determination of LOWLIM and HIGHLIM.                                 |

| Figure 4.8: Constructing a 'special' DLB communication, in which only specific   |

| processors will be involved in the internal communications                       |

| Figure 4.9: Example from APPLU_1.4 in which some of the communications of        |

| the implicitly partitioned variables PHI1 and PHI2 have been converted into      |

| DLB communications                                                               |

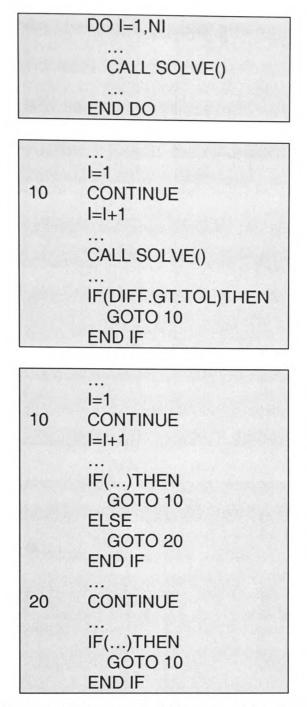

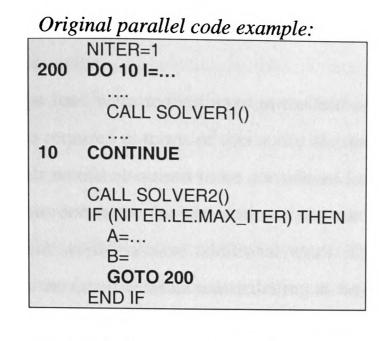

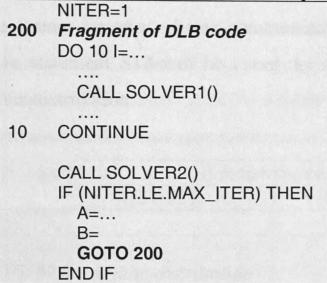

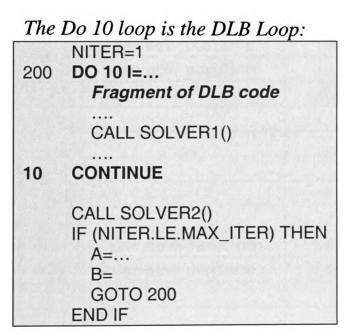

| Figure 4.10: Possible DLB Loops, where most of the processing is performed       |

| inside the loop 192                                                              |

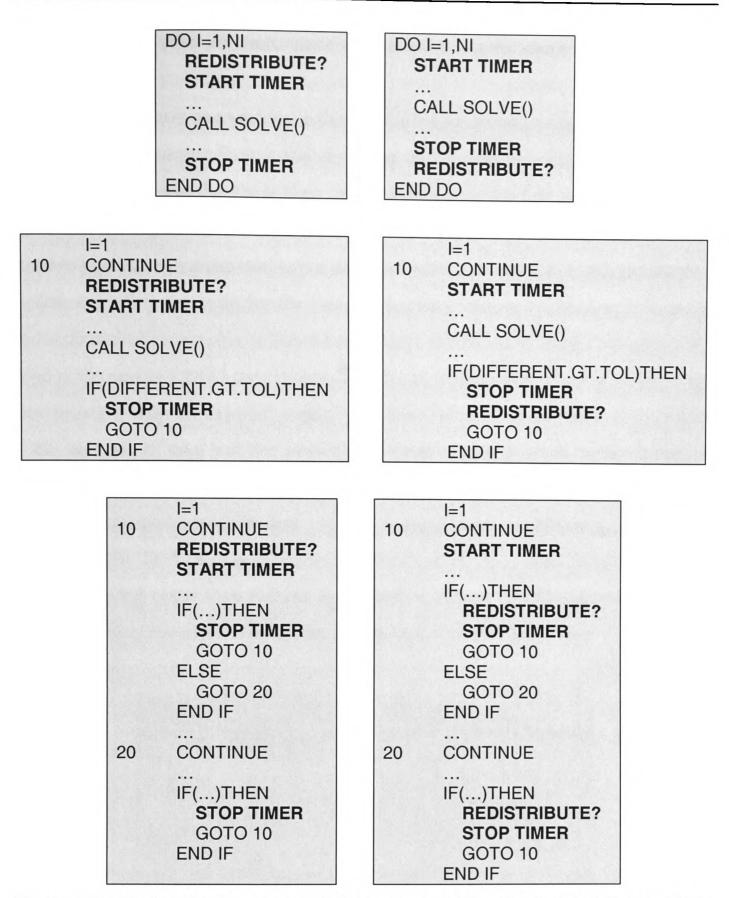

| Figure 4.11: Placing the timers around the code containing the load imbalance,   |

| where REDISTRIBUTE? involves determining whether or not to redistribute          |

| the load + code to migrate the load                                              |

| Figure 4.12: Example in which the load is not redistributed on the first or last |

| iteration unnecessarily194                                                       |

| Figure 4.13: Redistribution only occurs at the beginning of an iteration         |

| Figure 4.14: Partitioned data that is used after redistribution will need to be  |

| migrated                                                                         |

| Figure 4.15: Construction of migration calls using information relating to the   |

| migrated data                                                                    |

| Figure 4.16: The processor partition range limits of a particular dimension are  |

|                                                                                  |

updated using CAP\_DLB\_REASSIGNLOWHIGH after migrating the load in that dimension, after which CAP\_DLB\_NEW2OLD\_LIMITS is used to

| update the internal processor partition range limits used in the DLB utilities.      |

|--------------------------------------------------------------------------------------|

|                                                                                      |

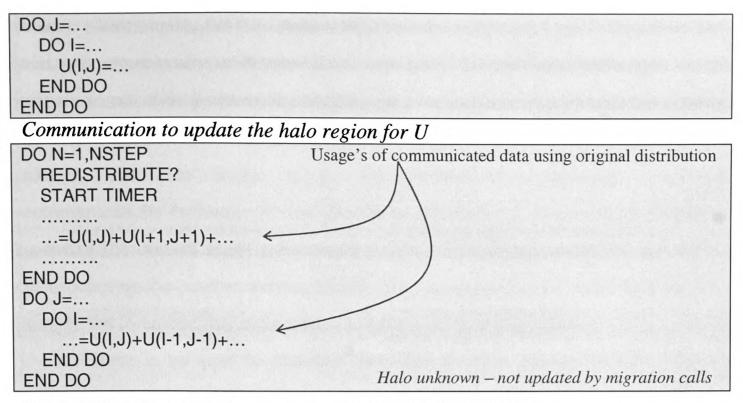

| Figure 4.17: Code extract showing usage of halo data after redistribution 202        |

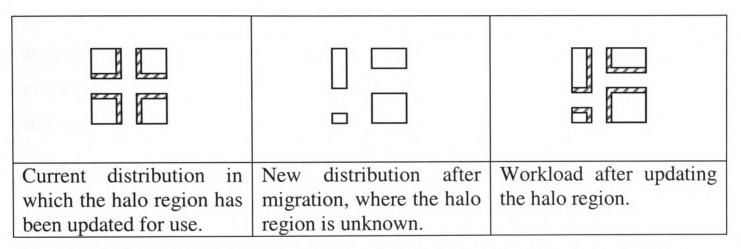

| Figure 4.18: Illustration showing the need to update the halo region after data      |

| migration                                                                            |

| Figure 4.19: Statements executed before redistribution need to be examined for       |

| halo communications that may be duplicated                                           |

| Figure 4.20: Illustration showing how to identify communications that need to be     |

| duplicated. Communications occurring after redistribution do not need to be          |

| duplicated, as these communications use the newly updated data distribution.         |

|                                                                                      |

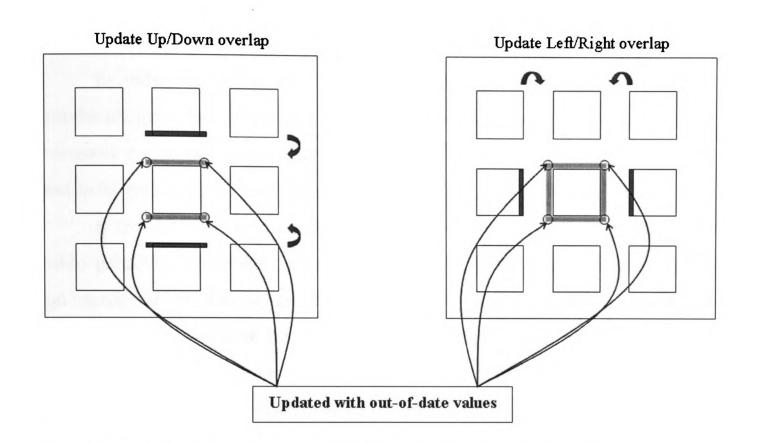

| Figure 4.21: Result when communications are duplicated with no regard to their       |

| order of execution. When duplicates of Up/Down communications are placed             |

| before Left/Right communications then out-of-date values are used                    |

| Figure 4.22: Example from ARC2D in which there is no halo communication to           |

| duplicate, since the halo region is initially assigned on each processor 206         |

| Figure 4.23: Example illustrating the need to migrate a scalar variable that is      |

| assigned and used between given processor partition range limits                     |

| Figure 4.24: Shows an extract of sample code in which the highlighted code           |

| represents the DLB code that has been inserted into it, and a brief                  |

| explanation of the inserted statements                                               |

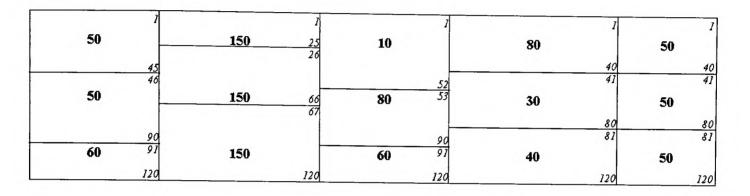

| Figure 4.25: The processor timings and processor partition range limits of the first |

| iteration for a heterogeneous 3x3 processor topology (based on a cluster of          |

| workstations) that has been mapped evenly onto a 1000x1000 JACOBI mesh               |

| code application                                                                     |

| Figure 4.26: The new distributions, the associated processor timings, partition      |

| range limits and workloads are shown for iteration 2                                 |

| Figure 4.27: The new distributions, the associated processor timings, partition      |

| range limits and workloads are shown for iteration 3                                 |

| Figure 4.28: The new distributions, the associated processor timings, partition      |

| range limits and workloads are shown for iteration 4                                 |

| Figure 4.29: The processor timings, partition range limits and workloads are         |

| shown for iteration 16                                                               |

| Figure 4.30: A discretised model of the Earth is evenly partitioned onto 3x3         |

|--------------------------------------------------------------------------------------|

| processors (each represented by a different shading), where each processor           |

| owns a varying depth of ocean upon which to compute on                               |

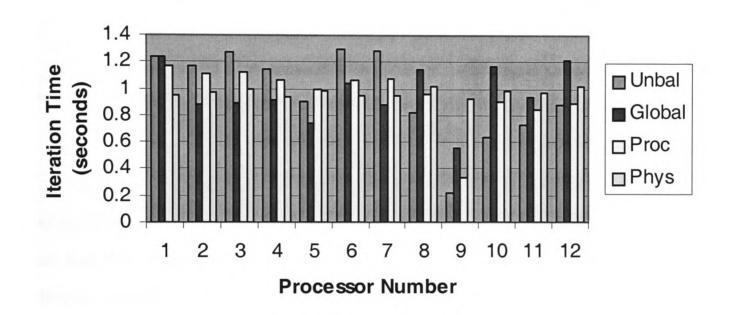

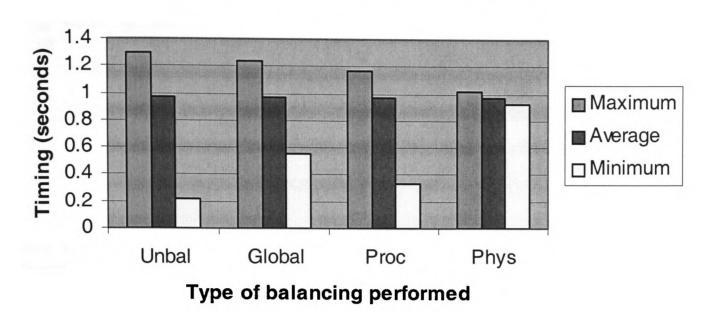

| Figure 4.31: Processor timings at Iteration 16 for various types of load balancing   |

| techniques, where Processor 9 contains Europe and Russia                             |

| Figure 4.32: Statistical measurements for the various load balancing techniques at   |

| Iteration 16                                                                         |

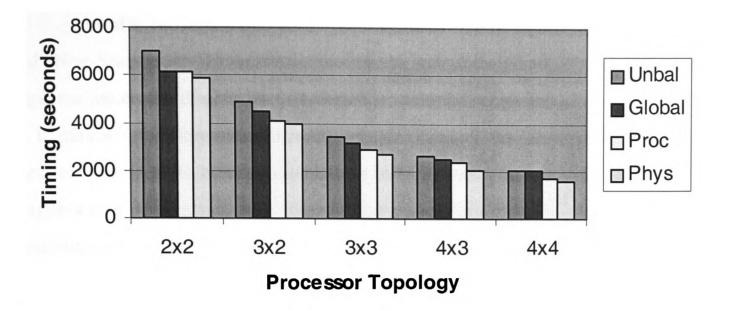

| Figure 4.33: The execution times (CPU+Redistribution time) for 2000 Iterations       |

| using different load balancing techniques on various processor topologies.           |

|                                                                                      |

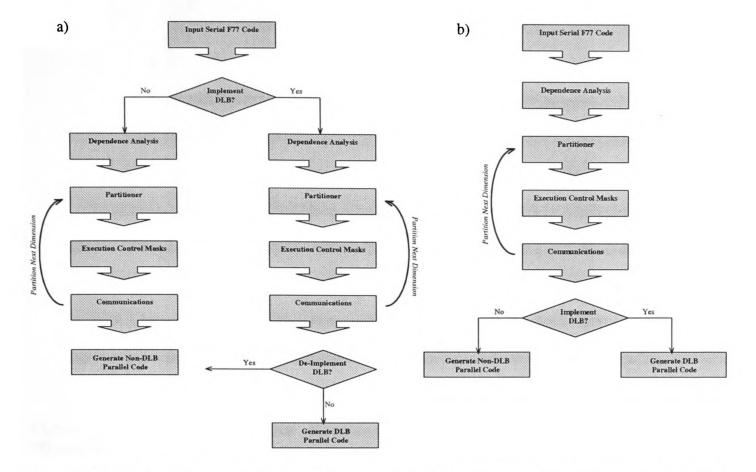

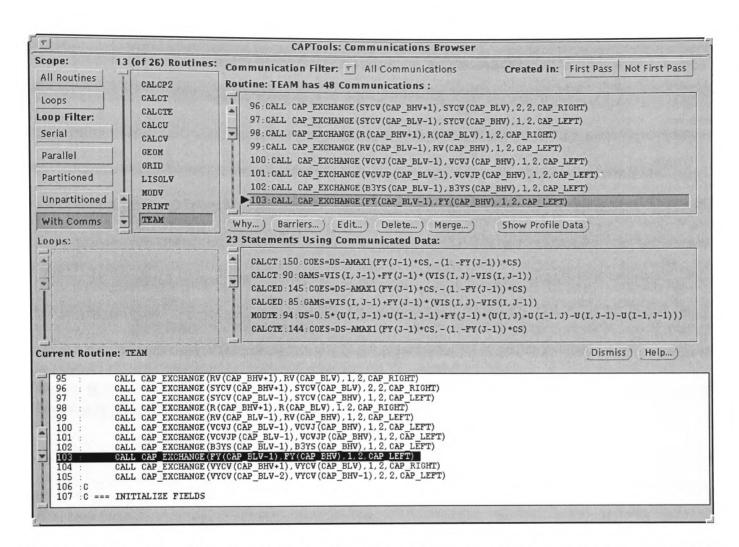

| Figure 5.1: Pictorial representation of the parallelisation process when the user is |

| given the option to implement DLB a) from the onset, or b) at the end of the         |

| parallelisation process                                                              |

| Figure 5.2: The Code Generator window (see Figure B.46) is modified to include       |

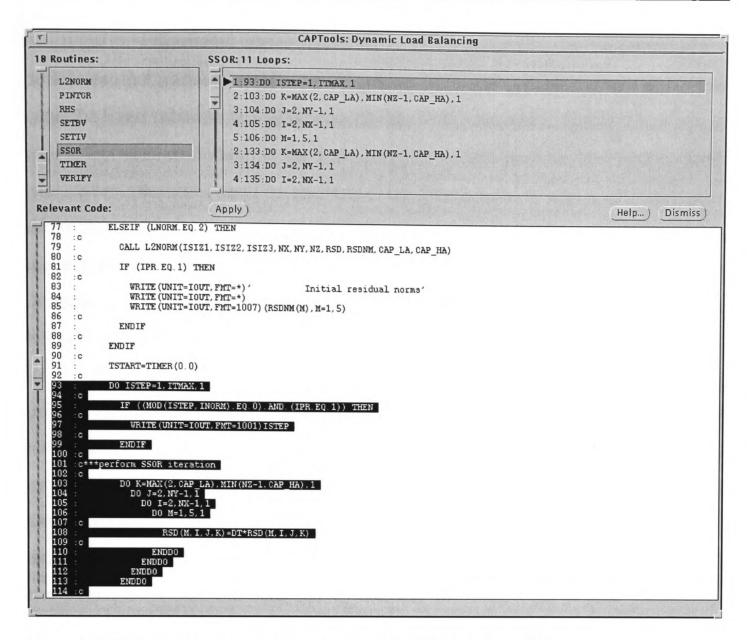

| the "Dynamic Load Balance" button as part of the functionality of                    |

| CAPTools                                                                             |

| Figure 5.3: The DLB Browser window used to select the imbalanced loop 231            |

| Figure 5.4: New data structure needed to store information relating to the current   |

| and previous partitions of a particular routine                                      |

| Figure 5.5: The major components involved in automatically generating DLB            |

| parallel code using CAPTools                                                         |

| Figure 5.6: The basic pseudo algorithm used to identify those communications         |

| that may need to be converted into DLB communications                                |

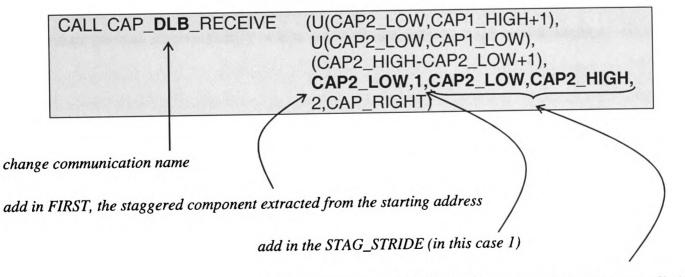

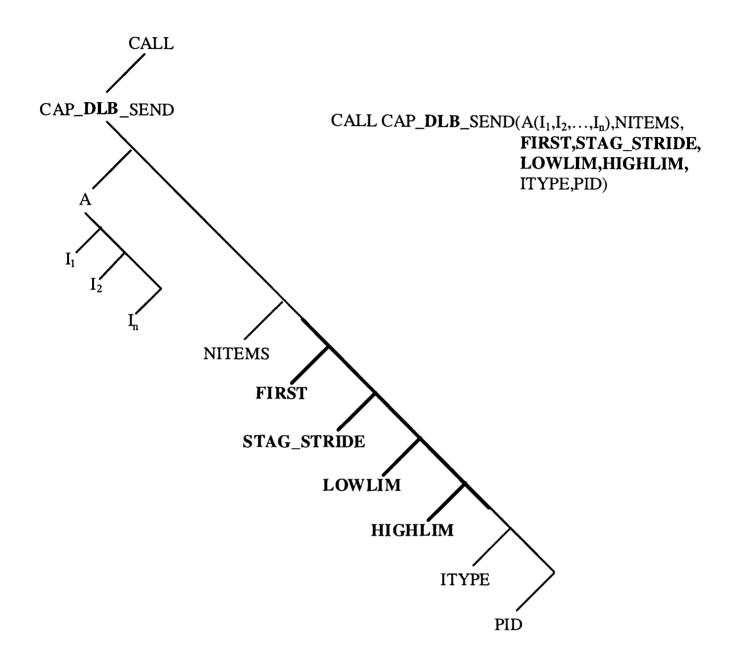

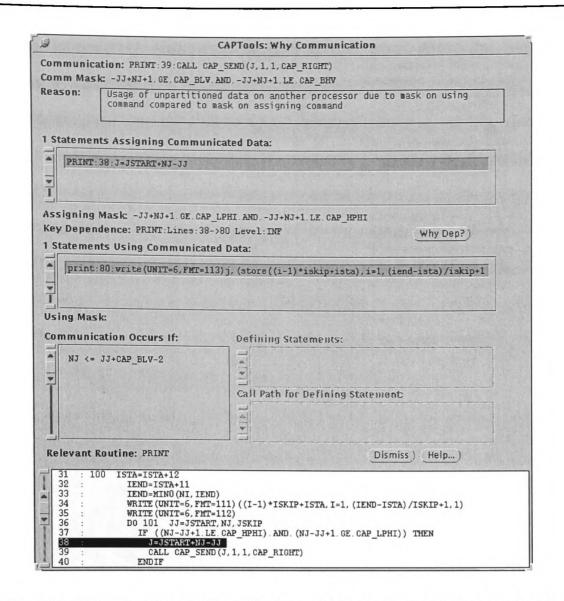

| Figure 5.7: Example communication call (CAP_BSEND) that has been converted           |

| into a DLB communication call, where its associated tree structure is also           |

| shown                                                                                |

| Figure 5.8: Code used to convert a communication call name into a DLB call,          |

| where the type of communication is retained                                          |

| Figure 5.9: Code used to identify the location in the communication tree structure   |

| at which to place the additional DLB parameters                                      |

| Figure 5.10: The main fields of the PARTITION data structure in a given routine      |

| that are used to automatically convert a given communication into a DLB              |

| communication                                                                        |

| Figure 5.11: Code used to traverse to the partitioned index in the communication     |

|--------------------------------------------------------------------------------------|

| starting address (where the partition INDEX > 0)                                     |

| Figure 5.12: When communicated data is 1D-mapped (i.e. INDEX $\leq$ 0), the          |

| partitioned component in the communication starting address for the                  |

| Staggered Dimension can be extracted using EXTRACTEXPRESSION                         |

| (which uses SYMBOLICMOD and SYMBOLICDIV)                                             |

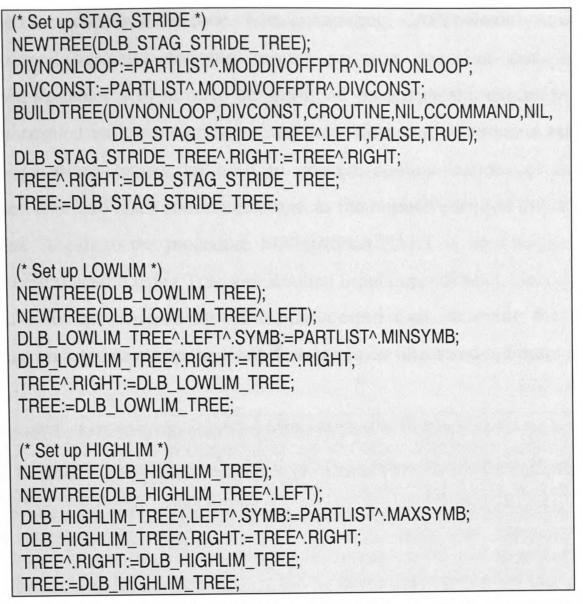

| Figure 5.13: The STAG_STRIDE, LOWLIM and HIGHLIM parameters can be                   |

| set up using the fields in the PARTITION record of the routine in which the          |

| communication is contained241                                                        |

| Figure 5.14: If the communicated data is not found in routine's partition list, then |

| an implicit partition may be found using FINDIMPLICPART, or the value of             |

| FIRST may be determined for use in 'special' DLB communications 242                  |

| Figure 5.15: Pseudo algorithm used to evaluate the communication 'offsets' that      |

| determine LOWLIM and HIGHLIM                                                         |

| Figure 5.16: Setting up the LOWLIM and HIGHLIM parameters when the                   |

| communicated data is implicitly partitioned, where any offsets determined in         |

| FINDIMPLICPART are included in the expression                                        |

| Figure 5.17: Setting up the FIRST and STAG_STRIDE parameters for a 'special'         |

| DLB communication                                                                    |

| Figure 5.18: Example setting up the parallel code to execute in DLB mode247          |

| Figure 5.19: Inserting a new command at the end of the declaration list for a        |

| specified routine                                                                    |

| Figure 5.20: Identifying calls that determine the processor partition range limits,  |

| which are used to construct the parameters needed for the call to                    |

| CAP_DLB_SETUPLIMITS248                                                               |

| Figure 5.21: The underlying DLB implementation code that is placed at the            |

| beginning of an iteration of the DLB Loop                                            |

| Figure 5.22: The code used to determine the block containing the fragment of         |

| underlying DLB implementation code                                                   |

| Figure 5.23: Example illustrating the need to consider the loop nesting when         |

| deciding where to place the code shown in Figure 5.21                                |

| Figure 5.24: Example illustrating the need to duplicate the communication in S4      |

| when the workload is redistributed at REDISTR. B (at the end of the DLB              |

| Loop) due to the usage of the variable T in statement S12                            |

| Figure 5.25: Example illustrating a code in which the redistribution occurs in the  |

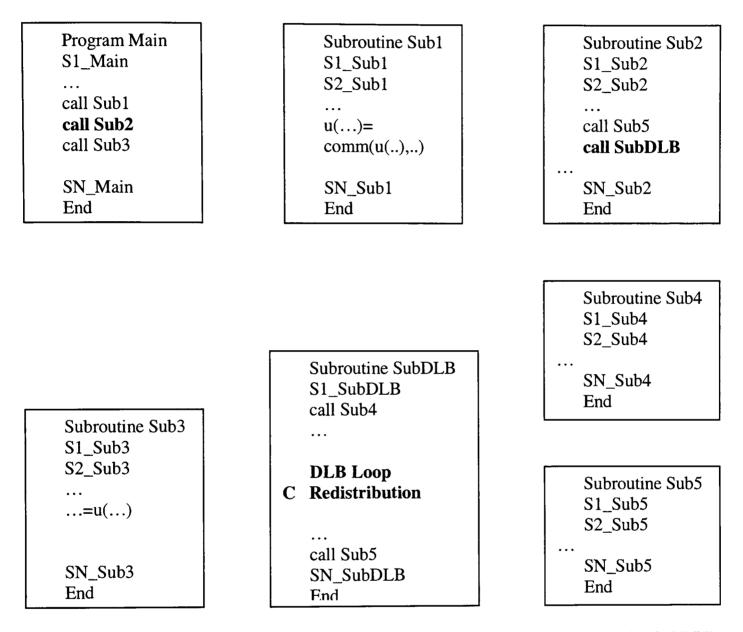

|-------------------------------------------------------------------------------------|

| SubDLB, which is called from Sub2 that is called from the Main program.             |

|                                                                                     |

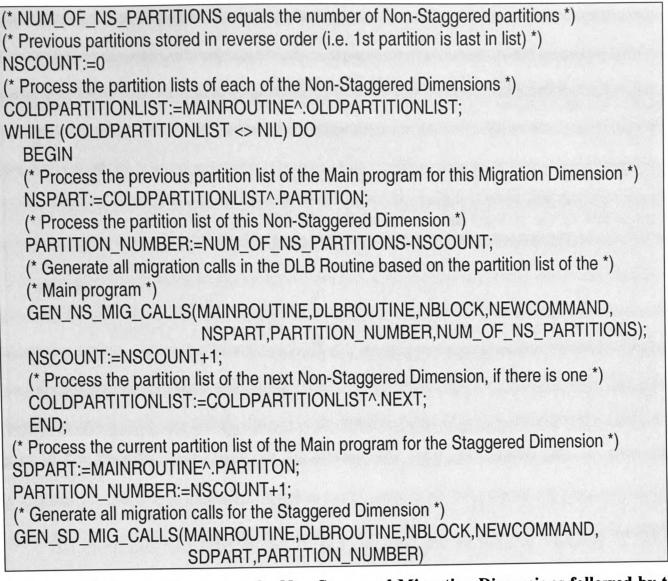

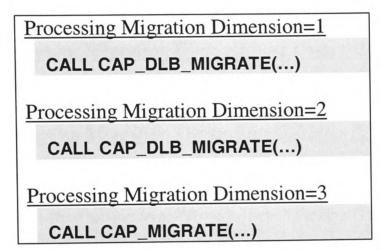

| Figure 5.26: Code used to process the Non-Staggered Migration Dimensions            |

| followed by the Staggered Dimension, where all of the migration calls are           |

| generated for the processed dimension along with the call to update that            |

| dimensions processor partition range limits                                         |

| Figure 5.27: Pseudo code used to determine the new call name for a converted        |

| communication                                                                       |

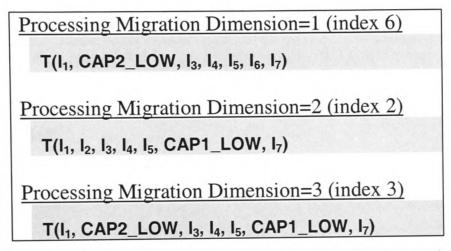

| Figure 5.28: Example illustrating the migration call name for the variable T that   |

| has been partitioned as shown258                                                    |

| Figure 5.29: Example illustrating the starting address for the migrated variable T. |

|                                                                                     |

| Figure 5.30: The pseudo algorithm used to determine the starting address for the    |

| migrated variable T                                                                 |

| Figure 5.31: Example illustrating the values of START_IND, STRIDE,                  |

| STAG_IND and STAG_STRIDE for the migrated variable T, along with the                |

| pseudo algorithm used to determine these parameters                                 |

| Figure 5.32: Example illustrating the values of S and NS for the migrated variable  |

| T                                                                                   |

| Figure 5.33: The pseudo algorithm used to determine the values of S and NS 265      |

| Figure 5.34: Example illustrating the values of ITYPE and MD for the migrated       |

| variable T                                                                          |

| Figure 5.35: Final generated migration calls for the variable T                     |

| Figure 5.36: Example illustrating the starting address for the migrated variable T  |

| that is 1D-mapped, which is identical to the starting address shown in Figure       |

| 5.29 for when T is not 1D-mapped                                                    |

| Figure 5.37: The pseudo algorithm used to determine the starting address for the    |

| migrated variable T that is 1D-mapped                                               |

| Figure 5.38: The pseudo algorithm used to determine the values of S and NS when     |

| the migrated data is 1D-mapped (i.e. no longer in terms of partitioned index,       |

| but partitioned component)                                                          |

| Figure 5.39: Final generated migration calls when T is 1D-mapped                    |

| Figure 5.40: Classification used to identify overlap communications that may       |

|------------------------------------------------------------------------------------|

| potentially need to be duplicated                                                  |

| Figure 5.41: Example illustrating that only the first of the two identical         |

| communications need to be considered for duplication                               |

| Figure 5.42: The different phases used to identify overlap communications to be    |

| duplicated                                                                         |

| Figure 5.43: Pseudo code used to process all of the predominating blocks of the    |

| DLB Loop head block                                                                |

| Figure 5.44: Pseudo code used to recursively process every calling routine and its |

| callers                                                                            |

| Figure 5.45: Examination of processed statement in FINDPREDLBCOMMS                 |

| (instances from which duplicable communications can be identified) 278             |

| Figure 5.46: Example DO Blocks that contain communication statements and non-      |

| communication statements                                                           |

| Figure 5.47: Examples of possible usage statements that require data to be         |

| communicated                                                                       |

| Figure 5.48: Pseudo code used to determine whether an identified communication     |

| needs to be duplicated                                                             |

| Figure 5.49: Example illustrating that the decision to duplicate an identified     |

| communication can be inherited by predominating communications                     |

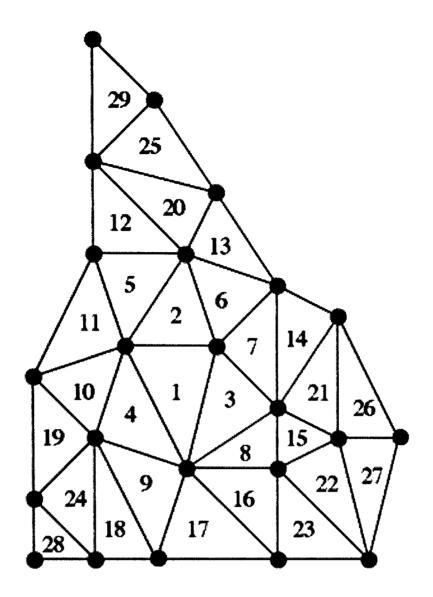

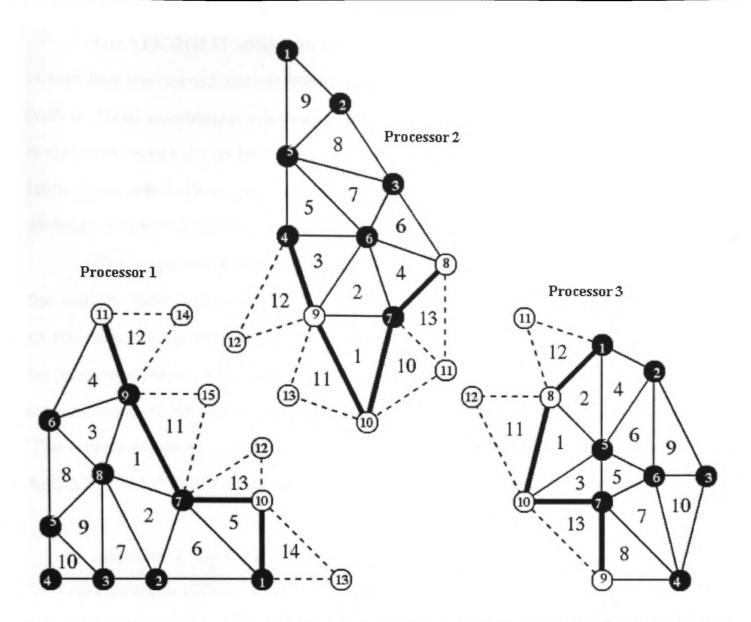

| Figure 6.1: Example of an unstructured mesh                                        |

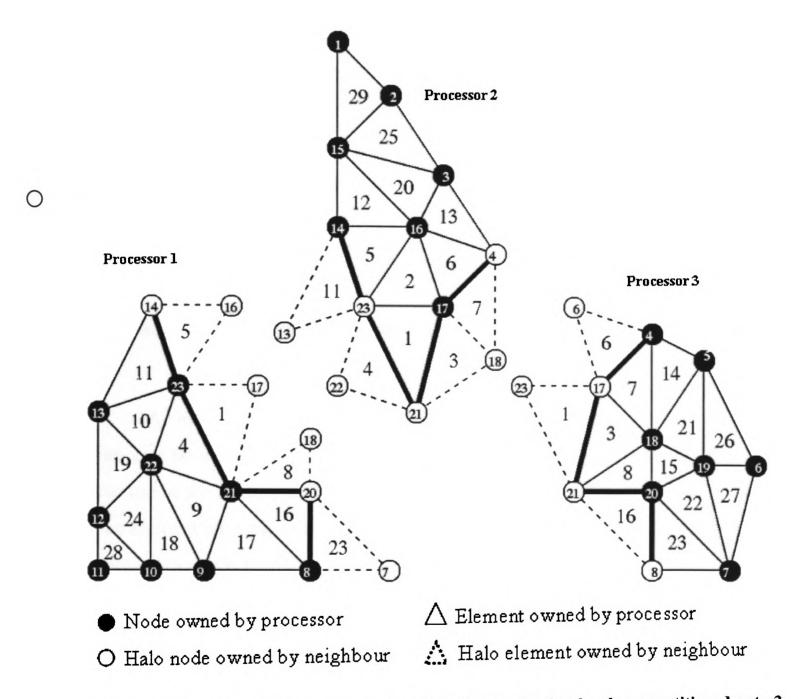

| Figure 6.2: Example of the unstructured mesh in Figure 6.1 that has been           |

| partitioned onto 3 processors, where global numbering is used                      |

| Figure 6.3: The partitioned unstructured mesh (shown in Figure 6.2) with local     |

| numbering used                                                                     |

| Figure 6.4: Sample code and the inspector loop used to set up the communication    |

| set needed to update data in the halo region in which a local numbering            |

| scheme has been used                                                               |

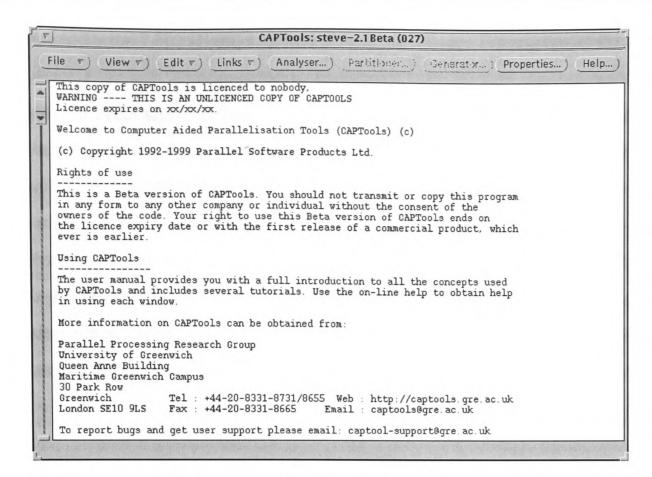

| Figure A.1: The main CAPTools GUI window, used to parallelise serial Fortran       |

| 77 codes                                                                           |

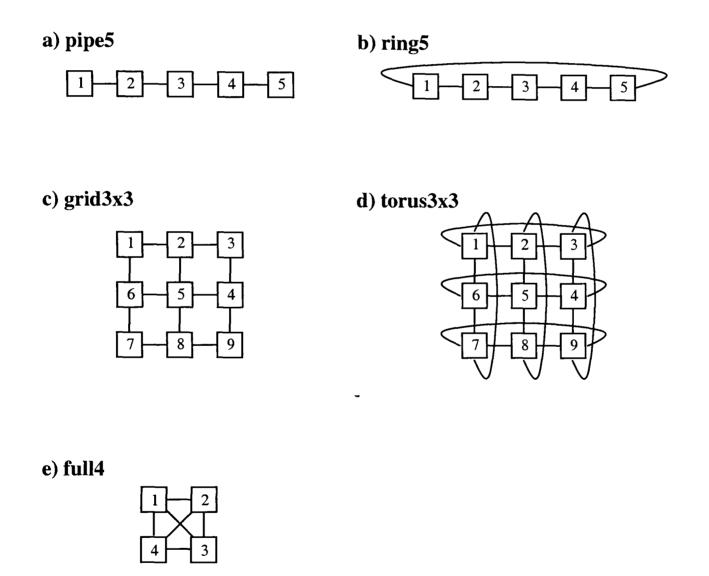

| Figure A.2: The different processor topologies used to represent the processor     |

| configuration, along with part of the necessary terminology used at runtime        |

| to execute the parallel code                                                       |

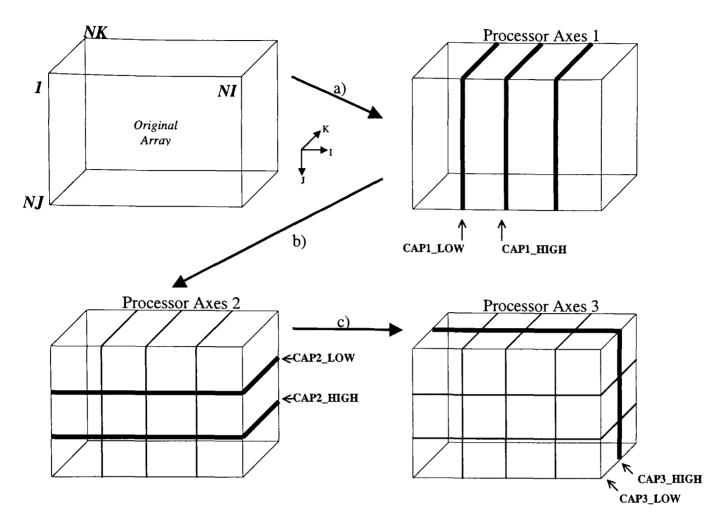

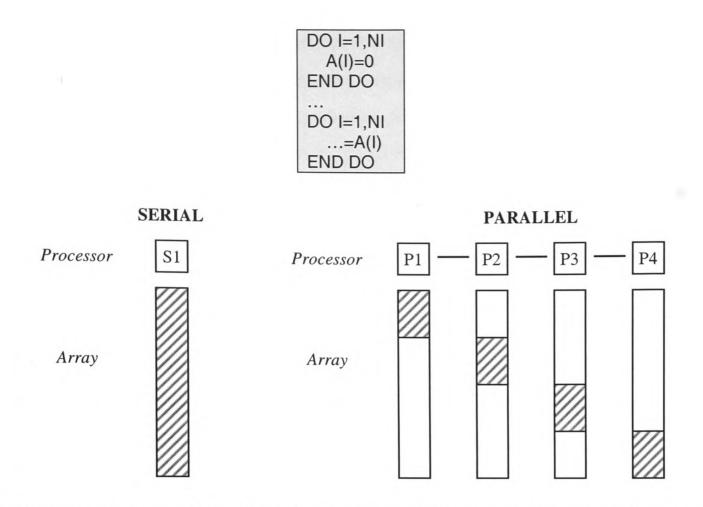

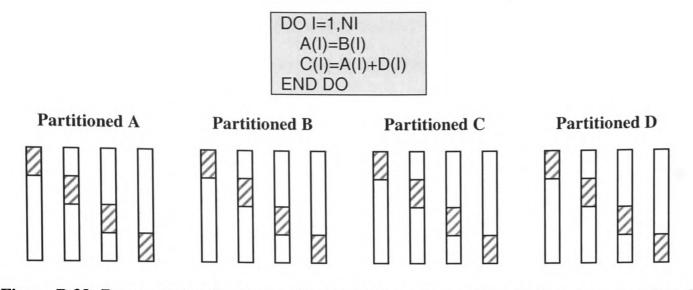

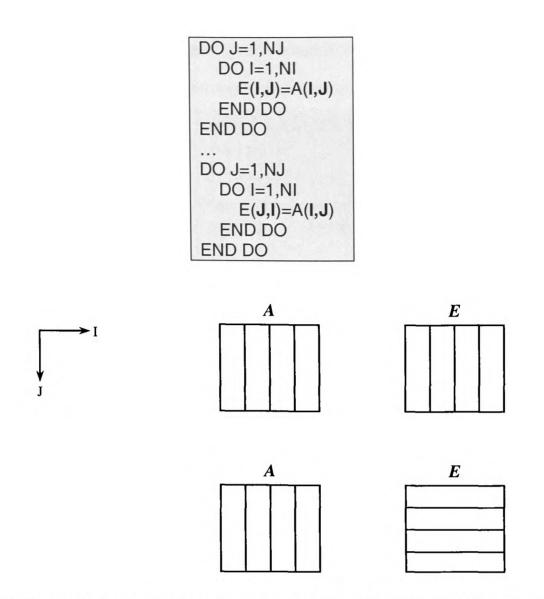

| Figure A.3: An example of an array that has a) been partitioned firstly the I       |

|-------------------------------------------------------------------------------------|

| direction; b) then partitioned secondly in J direction; and c) finally              |

| partitioned in the K direction. The processor axes and partition range limits       |

| are shown for each of the different partitions                                      |

| Figure A.4: Example demonstrating the initialisation of a parallel code given the   |

| specified processor configuration                                                   |

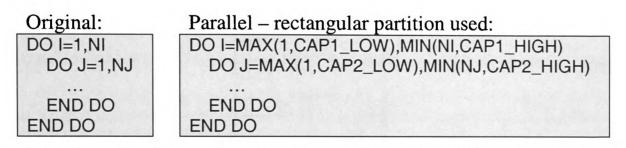

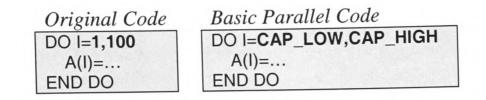

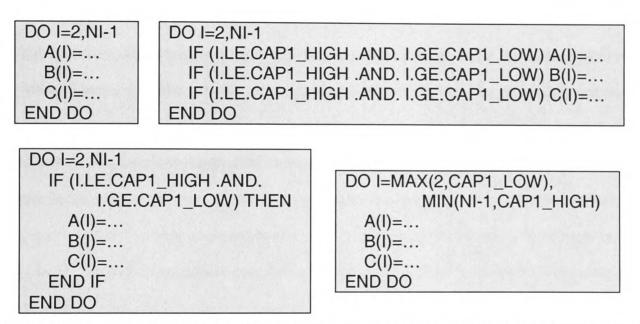

| Figure A.5: The original loop alongside the parallel loop in which rectangular      |

| partitions have been used                                                           |

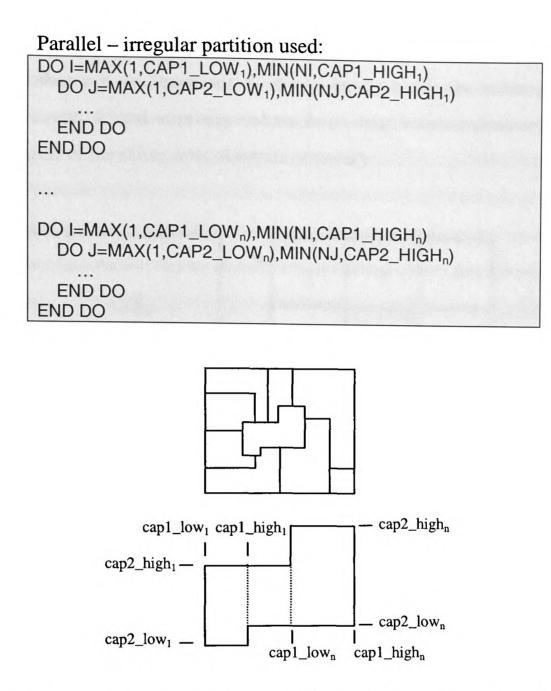

| Figure A.6: The parallel loops that are needed instead of the original loop when a  |

| non-rectangular partition has been used. Each loop represents a rectangular         |

| area within the sub-domain of a processor (which can be seen for the middle         |

| processor's first and last rectangular areas)                                       |

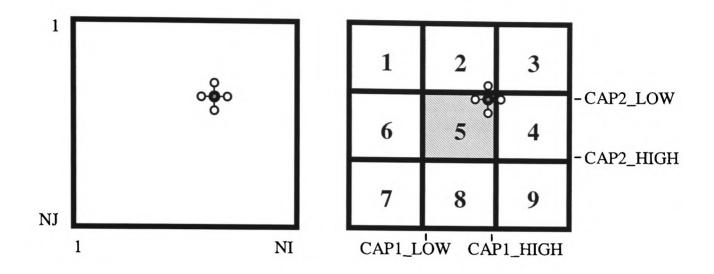

| Figure A.7: A 5-point stencil used on the original domain (in serial) and with a 2D |

| partition, where the processor partition range limits have been shown for           |

| Processor 5. Neighbouring cells are needed on each processor when                   |

| applying the stencil to boundary cells                                              |

| Figure A.8: Updating the processor halo region with values stored on                |

| neighbouring processors                                                             |

| Figure A.9: Sample code in which communications are required. The first             |

| example involves using data in the halo region, the second deals with I/O,          |

| and the third requires a global summation                                           |

| Figure A.10: Sequence of communicating that reduces the number of                   |

| communications required. Communicate in the direction of those dimensions           |

| that were partitioned first, enabling communication of already communicated         |

| data                                                                                |

| Figure A.11: Example illustrating the communication of corner points when           |

| updating the halo region                                                            |

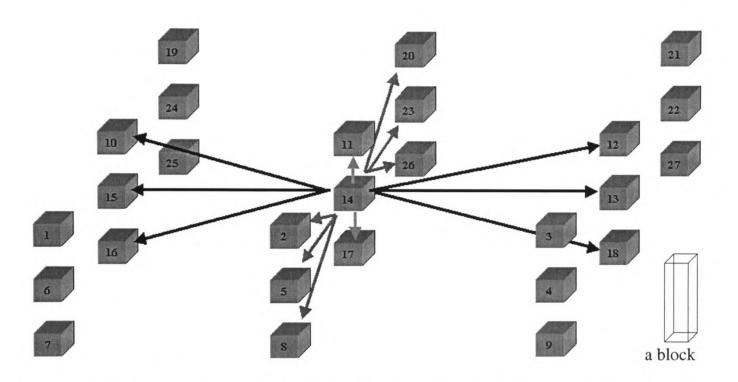

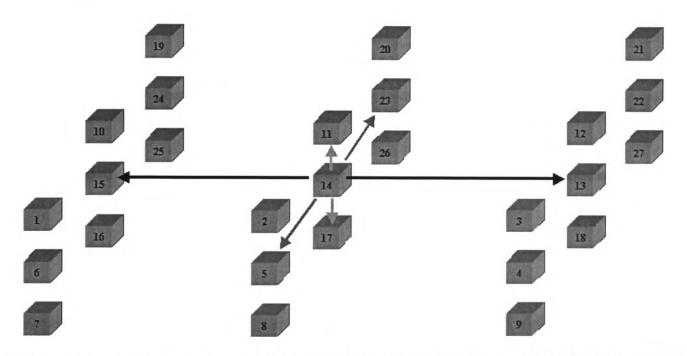

| Figure A.12: A 3D mesh example showing the communication topology for               |

| Processor 14, which only needs to communicate with its immediately                  |

| neighbouring processors (15 and 13 in the Left/Right direction, 11 and 17 in        |

| the Up/Down direction, and 5 and 23 in the Back/Forth direction)                    |

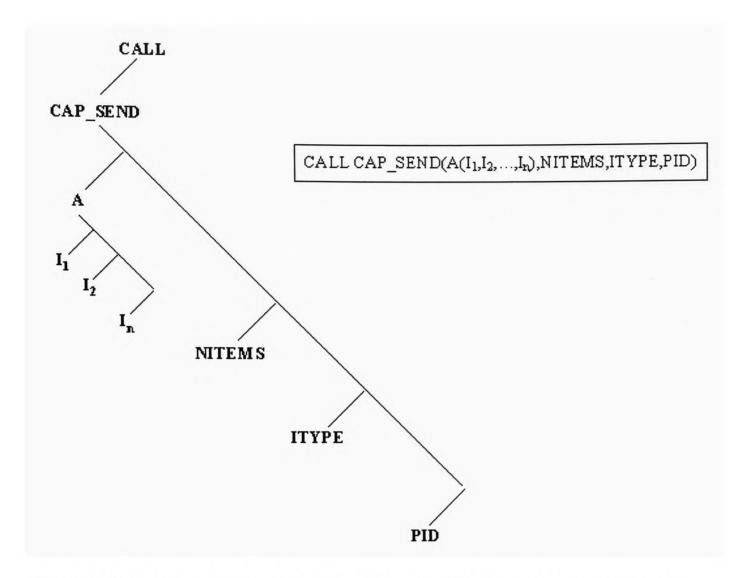

| Figure A.13: The basic communication calls used by CAPTools to send and             |

| receive NITEMS of A which is of data type ITYPE, in the communication               |

| direction PID                                                                       |

| Figure A.14: Examples of paired communications used to communicate NI and         |

|-----------------------------------------------------------------------------------|

| update the upper halo region of the array T                                       |

| Figure A.15: Update of the upper halo region on every processor by receiving the  |

| lower boundary value from the Right neighbour                                     |

| Figure A.16: An Exchange communication call, and an example, which is used to     |

| exchange data between two neighbouring processors                                 |

| Figure A.17: A 1D array that has been partitioned, along with a 2D array that has |

| been partitioned in index 1, and alternatively in index 2. The lower halo         |

| region is updated using the upper boundary of a neighbouring processor. An        |

| individual cell is communicated in the first example, a column of cells in the    |

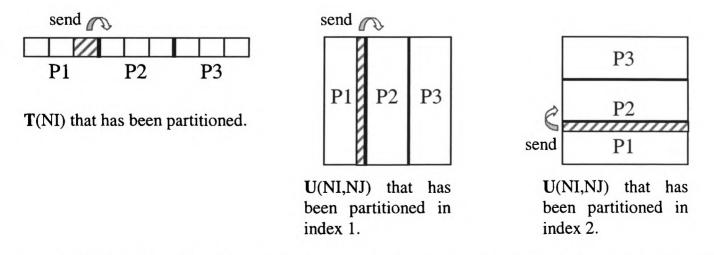

| second, and a row of cells (contiguous in memory) in the final example 326        |

| Figure A.18: Buffered communication calls, and some examples relating to the 2D   |

| problems shown in Figure A.17                                                     |

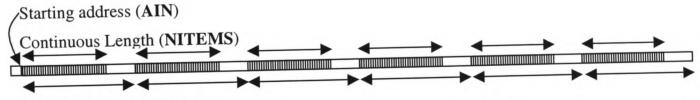

| Figure A.19: Representation of communicated data in 1D memory, where a            |

| NITEMS of continuous data is communicated NSTRIDE times from the                  |

| given starting address                                                            |

| Figure A.20: The Exchange communications that are used to update the halo         |

| regions on each processor in Figure A.8, where the width of the halo region       |

| is 1                                                                              |

| Figure A.21: Example showing when it is necessary to communicate a single         |

| plane at a time. The communicated data is not contiguous in more than one         |

| dimension                                                                         |

| Figure A.22: BROADCAST utilities, and an example in which partitioned data is     |

| assigned in several instances                                                     |

| Figure A.23: Example illustrating how a combination of Send/Receive               |

| communications can be used to broadcast data to neighbouring processors.          |

|                                                                                   |

| Figure A.24: Example in SUM is the summation of the array T, which is             |

| partitioned. After each processor calculates their local value of SUM, the        |

| commutative adds these together and broadcasts the value to all processors        |

| involved, such that each processor has the global value of SUM after the          |

| commutative                                                                       |

| Figure A.25: Scripts used to compile and execute a CAPTools generated parallel    |

| code                                                                              |

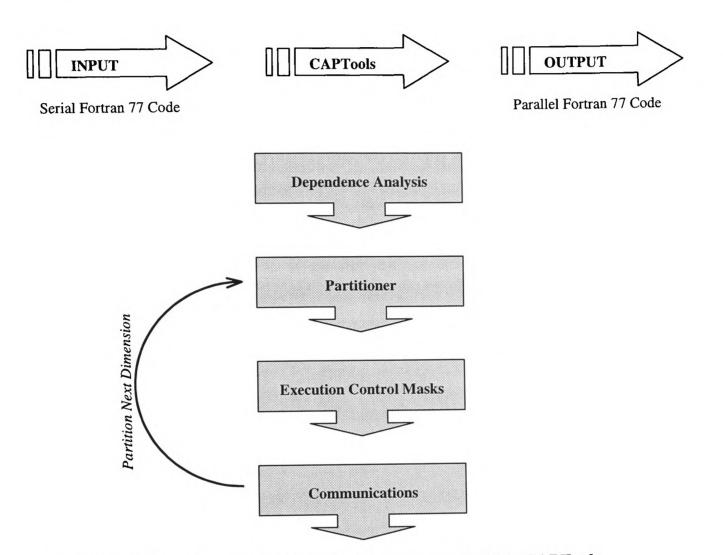

| Figure B.1: Representation of the parallelisation stages used within CAPTools.336  |

|------------------------------------------------------------------------------------|

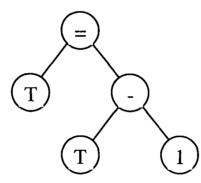

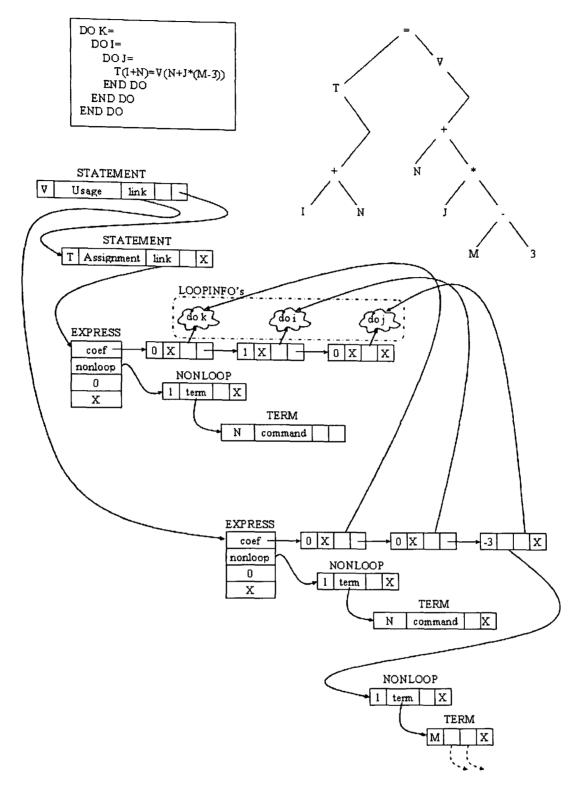

| Figure B.2: A parse tree within CAPTools that represents an assignment statement   |

| (involving integers)                                                               |

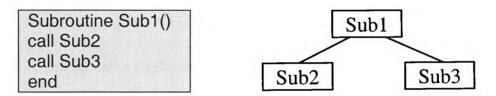

| Figure B.3: Sample code with the associated call graph                             |

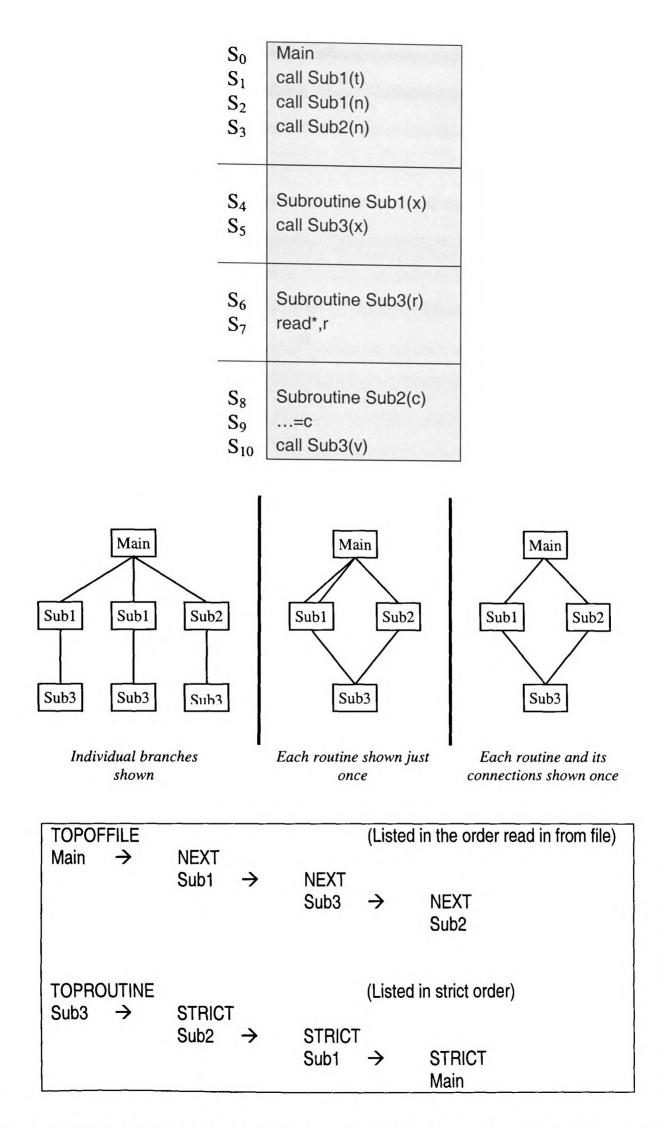

| Figure B.4: Example demonstrating that the value of t does not always equal the    |

| value of n. The sample code and its call graph are shown (in various degrees       |

| of simplicity). A demonstration of how the routines in this example would be       |

| processed is also shown                                                            |

| Figure B.5: Example of the Call Graph window in CAPTools showing 26                |

| routines                                                                           |

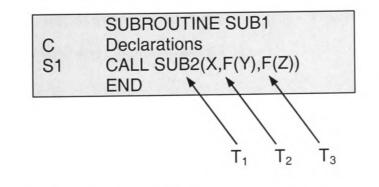

| Figure B.6: Example illustrating the CALLS data structure for the routine SUB1,    |

| in which a call to SUB2 is made (whose parameters include calls to the             |

| function F)                                                                        |

| Figure B.7: Pseudo code used to interprocedurally traverse the call graph 342      |

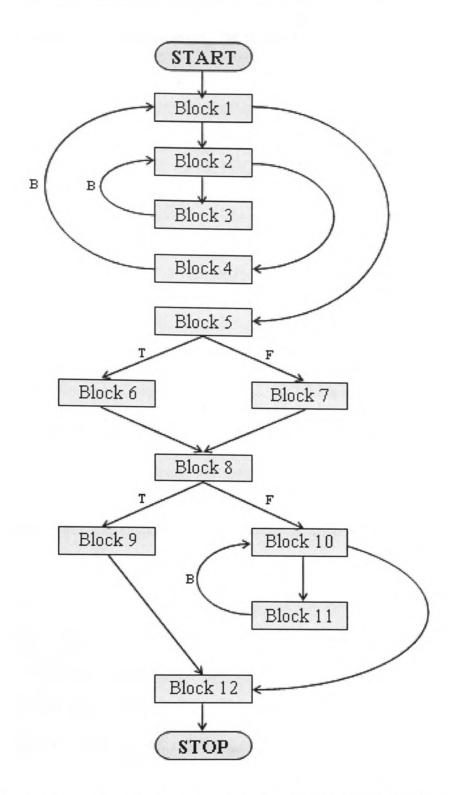

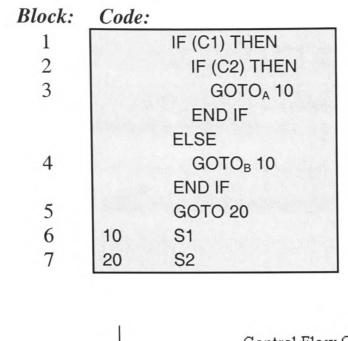

| Figure B.8: Code to demonstrate control flow                                       |

| Figure B.9: Control Flow Graph for example given in Figure B.8 above (T=True,      |

| F=False, and B=Backlink)                                                           |

| Figure B.10: Pseudo code used to traverse every statement in the input code 345    |

| Figure B.11: Pseudo code showing a depth first search of the basic blocks          |

| (traversing through each block just once in this case)                             |

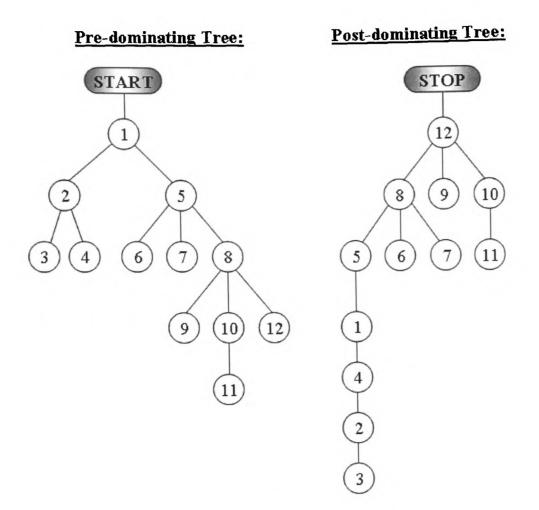

| Figure B.12: Predominator tree and Postdominator tree for the CFG in Figure B.9,   |

| where each block has one immediate predominator and postdominator block.           |

| All other dominators are found by traversing up the tree                           |

| Figure B.13: Pseudo code used to traverse up the predominator graph within         |

| CAPTools                                                                           |

| Figure B.14: Code demonstrating that the outer loop is the iterative loop and the  |

| innermost loop is the I Loop                                                       |

| Figure B.15: The different types of dependencies. a:-true dependence; b:-anti      |

| dependence; c:-output dependence; and d:-control dependence                        |

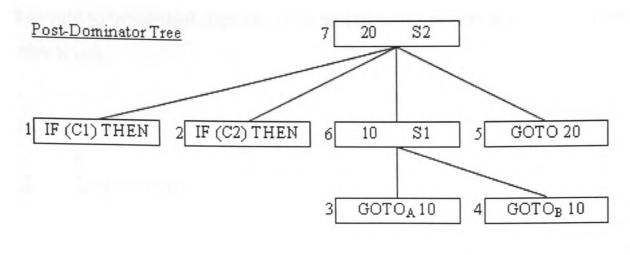

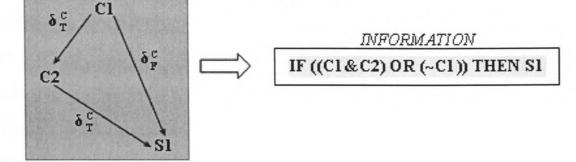

| Figure B.16: Sample code, with its control flow graph, postdominator tree, and the |

| control dependence graph for S1, which illustrates that S1 is dependent on         |

| C2 being True, given that C1 was previously True, OR that C1 was False.353         |

| Figure B.17: Pseudo algorithm used by CAPTools for control dependence              |

| calculation. Also shown is the application of this algorithm on the calculation    |

| of the control dependence graph for S1 in the example given in Figure B.16.      |

|----------------------------------------------------------------------------------|

|                                                                                  |

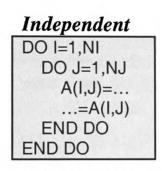

| Figure B.18: Example of a loop independent code, in which data is respectively   |

| assigned and used in the same iteration of the I and J loop                      |

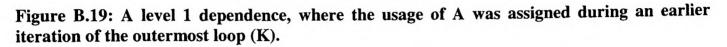

| Figure B.19: A level 1 dependence, where the usage of A was assigned during an   |

| earlier iteration of the outermost loop (K)                                      |

| Figure B.20: A level 2 dependence, where the usage of A was assigned in the      |

| previous iteration of the J loop                                                 |

| Figure B.21: Transformation used to Normalise a loop, where the loop starts from |

| L, ends at H, and has a step length of S                                         |

| Figure B.22: An un-normalised loop (starting at 3 and with a step length of 2),  |

| with the normalised version of the same loop (starting from 1 and with a step    |

| length of 1)                                                                     |

| Figure B.23: Example used to demonstrate dependence testing, where $X_a$ is the  |

| value of index X in an assignment, and $X_u$ is the value of index X in a usage, |

| from which the constraints can be constructed (shown in Table B.1) 357           |

| Figure B.24: Example of Level Infinity constraints for two independent loops     |

| surrounded by a common loop                                                      |

| Figure B.25: Example where the inference engine and logical substitution is used |

| in dependence testing, where both values of K must be proved false for any       |

| test                                                                             |

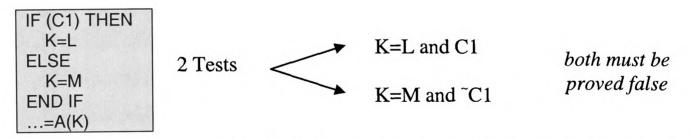

| Figure B.26: Example of the Dependence Graph window within CAPTools, along       |

| with the Statement and Dependence Filter options selected (from which the        |

| user can select which dependencies to view)                                      |

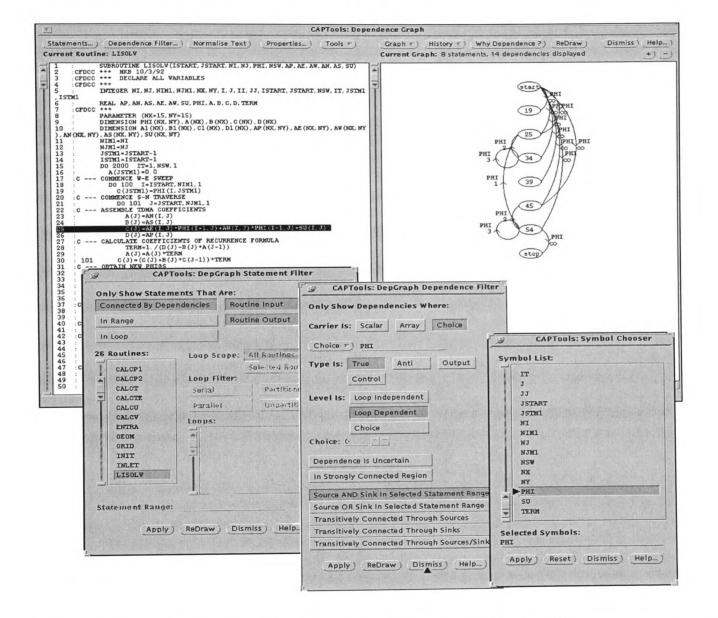

| Figure B.27: Sample code in which A is assigned in the calling routine and used  |

| in the called routine (as B)                                                     |

| Figure B.28: Example showing that the usage of A in Section 6 is not dependent   |

| upon the assignment of A in Section 1, as all of the usage range has been        |

| assigned in Sections 3, 4, and 5                                                 |

| Figure B.29: The parse tree and the symbolic data structures that are associated |

| with the given assignment statement. Note that X is used to represent a NIL      |

| entry                                                                            |

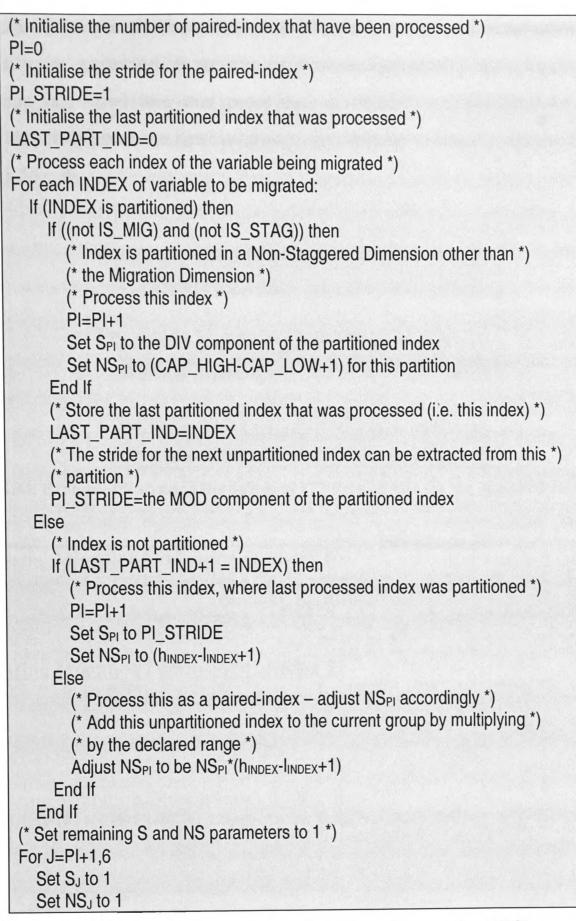

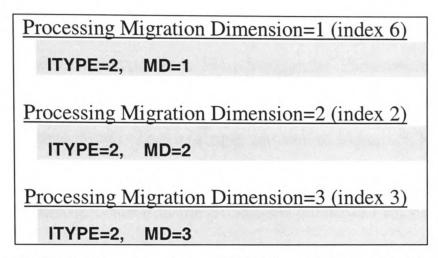

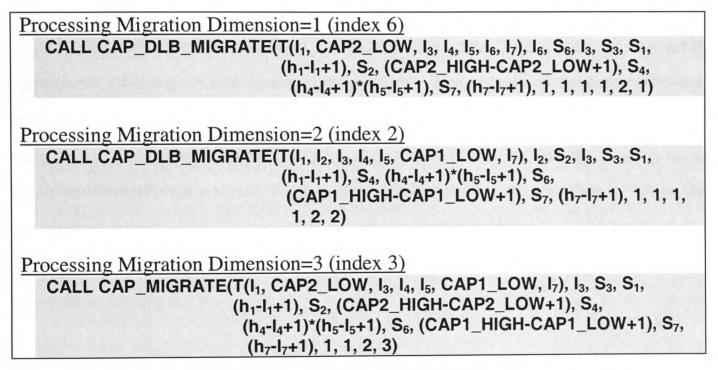

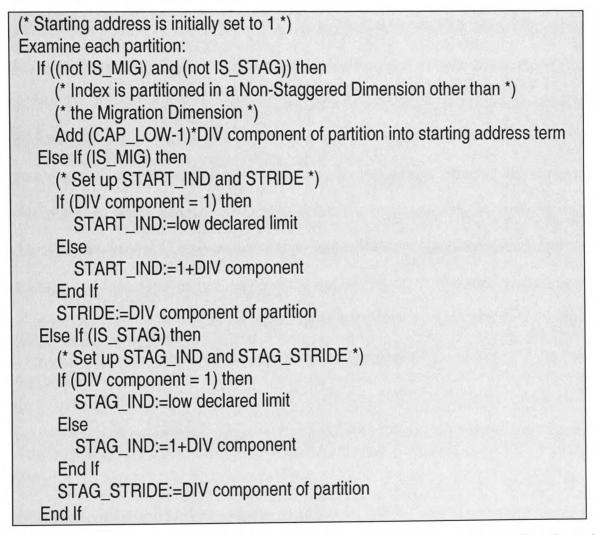

| Figure B.30: Representation of an array that is initialised in serial, and in parallel |